👉个人主页:highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

PCIE总线结构

PCI总线结构组成

HOST主桥

PCI总线

PCI设备

HOST处理器

PCI负载

PCIE体系结构组成

RC

Endpoint

Switch

PCIE层次结构

事务层

数据链路层

物理层

参考文章:PCI_Express体系结构导读

PCIE总线结构

PCI总线结构组成

PCIE是PCI发展而来的,我们先看一下PCI的总线结构,下图从《PCI Express体系结构导读》书中截取。把下图与计算机硬件体系结构的CPU-GPU-南桥-北桥结构对应一下,上面红框应该是集成在CPU中,下面的绿框集成在北桥中,剩下部分都是PCI设备或者PCI到其他总线的转换桥。这个集成方式不重要,不同的处理器系统会有差别,这里对应一下是为了有个直观的展示。

上图与PCI总线相关的模块包括:HOST主桥(即Host to PCI主桥,也称PCI主桥、PCI总线控制器)、PCI总线、PCI设备、PCI桥(即PCI to PCI主桥)、PCI to其他总线桥。PCI总线由HOST主桥或PCI桥推出。HOST主桥与主存控制器在同一级总线上(就是CPU到北桥的系统总线),所以PCI设备可以通过DMA操作经HOST主桥访问主存。PCI设备的DMA操作需要与处理器系统的cache进行一致性操作(cache一致性是指在采用层次结构存储系统的计算机系统中,保证高速缓冲存储器中数据与主存储器中数据相同机制,详见高速缓冲存储器一致性_百度百科 (baidu.com)),当PCI设备进行DMA操作时,cache一致性模块进行地址监听,并根据监听结果改变cache状态。

HOST主桥

Host主桥主要功能:1、隔离处理器系统的存储器域和PCI总线域;2、管理PCI总线域;3、完成处理器与PCI设备之间的数据交换(包括CPU访问PCI设备的地址空间,PCI设备使用DMA机制访问主存储器)。

PCI总线

如上结构图所示,PCI总线x0连在HOST主桥x,PCI总线x1通过PCI桥x1连接在HOST主桥x,整个HOST主桥x下挂的叫一个总线树。总线树可以包括多条PCI总线(就是用PCI桥扩出来的总线)。PCI总线由HOST主桥或PCI桥管理,用来连接各类设备,如声卡、网卡、IDE接口卡等。

PCI设备

PCI设备在总线规范上被称为PCI Agent设备,PCI设备可以分为三类:

主设备:可以通过总线仲裁获得PCI总线控制权,主动向其他PCI设备或主存储器发起读写请求。

从设备:只能被动接收来自HOST主桥或其他PCI设备的读写请求。

桥设备:管理下游的PCI总线,并转发上下游总线之间的总线事务。

HOST处理器

严格来说,HOST处理器不是PCI总线结构的组成部分。HOST处理器可以通过HOST主桥,发起PCI总线的配置请求总线事务,并对PCI总线上的设备和桥片进行配置,注意,PCI总线树的直接管理者是HOST主桥,不是HOST处理器。HOST处理器是一个较为模糊的概念,在多核CPU中,所有core都可以通过HOST主桥访问其下的PCI总线树,但是在同一时间内,一颗PCI总线树有且只有一个HOST处理器。HOST处理器通过操作HOST主桥中设置的寄存器来管理PCI设备。

PCI负载

总线频率越高,能挂接的负载越少,但整条总线能提供的带宽越大。

PCIE体系结构组成

PCIE相对PCI的拓扑结构有了较大变化。PCI是并行总线型主从结构,同一条总线上的外部设备共享总线带宽,而PCIE采用了高速差分端到端传输,每条PCIE链路上只能连接两个设备。一个典型的PCIE拓扑结构如下,与PCIE结构相关的部件有RC、Switch、PCIE设备、PCIE to PCI桥:

RC

RC是PCIE体系结构中一个重要组成部件,同时RC也是一个概念比较模糊的部件。PCIE规范中并没有定义RC的实现细节,不同的处理器系统中,RC的实现有较大差异。有的处理器系统中,RC相当于PCIE主桥(类似于PCI的host主桥,主要完成存储器域到PCI总线域的地址转换),也有的处理器系统将PCIE主桥称为PCIE总线控制器,而在x86处理器系统中,RC除了包含PCIE总线控制器以外,还集成了一些PCI设备、RCRB(RC register block,由一系列管理存储器系统的寄存器组成)和event collector(处理来自PCIE设备的错误消息报文和PME消息报文)等组成部件。此外,处理器与RC连接的前端系统总线协议和电气特性一般与PCIE总线不兼容,所以RC还需要做信号协议与总线事务的转换。再外,再引入了虚拟化技术后,RC的实现变得更大复杂。

这里不过多研究RC的结构,大家只需要大致知道,它一般实现了一条内部PCIe总线(BUS 0),以及通过若干个PCIe bridge,扩展出一些PCIe Port,如下图:

Endpoint

就是PCIE的终端设备,比如SSD、网卡、显卡等。

Switch

由于PCIE采用的是点对点连接,所以若PCIE设备大于RC端口数量,则需要用switch进行端口扩展。一个标准的switch有一个上游端口和多个下游端口,上游端口与RC或其他switch的下游端口相连,下游端口可以与EP、PCIE to PCI桥或其他switch的上游端口相连。如下图:

对每个Switch来说,它下面的Endpoint或者Switch,都是归它管的。上游下来的数据,它需要甄别数据是传给它下面哪个设备的,然后进行转发;下面设备向RC传数据,也要通过Switch代为转发。因此,Switch的作用就是扩展PCIe端口,并为挂在它上面的设备(Endpoint或者Switch)提供路由和转发服务。每个Switch内部,也是有一根内部PCIe总线的,然后通过若干个Bridge,扩展出若干个下游端口,如下图所示:

PCIE层次结构

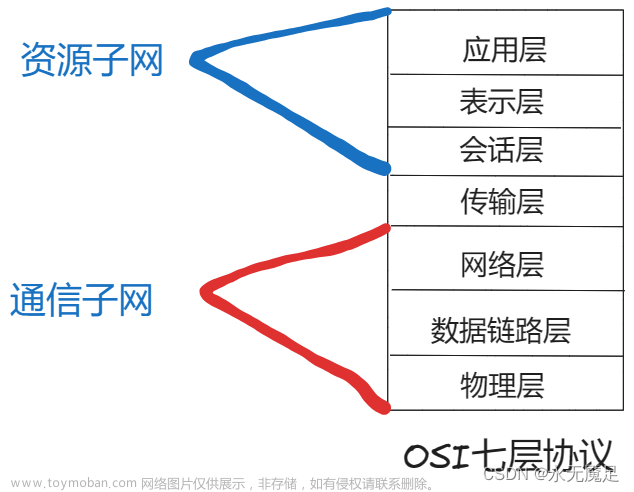

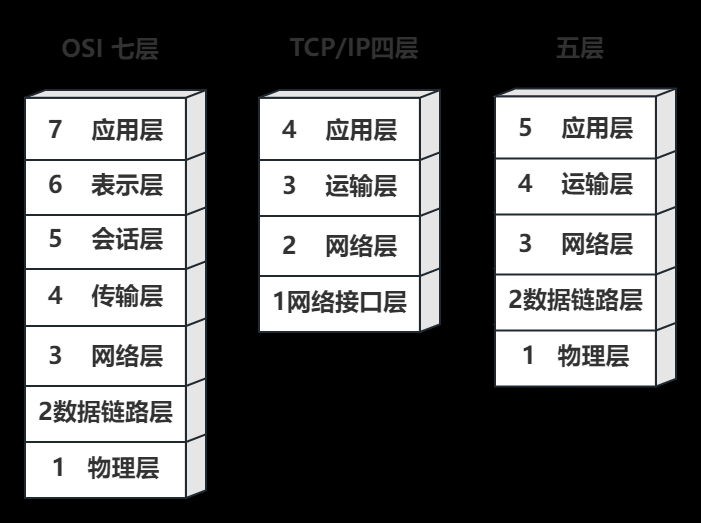

了解完PCIE的硬件拓扑结构之后,再来看一下PCIE的逻辑层次结构。由于PCIE采用了差分高速链路一对一传输,去掉了PCI中一些边带信号引脚,比如INTx、PME#,但这些信号不能说去掉就去掉,还是要传输的,于是PCIE采用了数据包packet的形式将原来带外信号进行带内传输,不同的数据报文,比如有真实数据载荷、控制信号、管理信号等一些报文,这些不同报文在传输时需要用到各种模块,为了使这些模块规范化,PCIE采用了和网络传输类似的分层结构,这些层次结构在PCIE中都是硬件实现。

PCIe定义了下三层:事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer,包括逻辑子模块和电气子模块),每层职能是不同的,但下层总是为上层服务的。分层设计的一个好处是,如果层次分得够好,接口版本升级时,硬件设计可能只需要改动某一层,其他层可以保持不动。RC、EP、switch都得分别实现这三层。如下图所示:

PCIe传输的数据从上到下,都是以数据包(Packet)的形式传输的,每层数据包都有其固定的格式。

事务层

事务层定义了PCIE总线使用的总线事务,大部分与PCI总线兼容。这些总线事务可以通过switch等设备传送到其他PCIE设备或RC。这一层的主要职责是创建(发送)或者解析(接收)TLP(Transaction Layer Packet)、流量控制、QoS、事务排序等。

数据链路层

数据链路层的主要职责是保证事务层下发的报文能可靠、完整地传送到对端的数据链路层。事务层报文将在此层被添加sequence number前缀和CRC后缀。数据链路层使用Ack/Nak协议来保证数据的可靠传输。另外数据链路层还定义了多种DLLP(Data Link Layer Packet)、ACK/NAK协议信息、流控、电源管理功能都是通过DLLP来传递。需要注意的是,DLLP虽然名字叫数据链路层报文,但他不是TLP报文加上前缀和后缀。具体DLLP格式后面会讲。文章来源:https://www.toymoban.com/news/detail-496781.html

物理层

物理层的主要职责是处理所有的Packet数据物理传输,发送端数据分发到各个Lane传输(Stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加扰(Scramble,目的是让0和1分布均匀,去除信道的电磁干扰EMI)和去扰(De-scramble),以及8b/10 b或128 b /130 b或其他方式的编码解码等。物理层还定义了LTSSM状态机,用来管理链路状态,并进行链路训练、链路恢复和电源管理(LTSSM的电源管理和DLLP的电源管理有什么不同?)另外,物理层定义了一些物理层专门的“序列”,有的地方称这些“序列”为PLP(physical layer packet),这些序列用于同步PCIE链路,并进行链路管理。注意,PCIE设备发送PLP和发送TLP的过程有所不同,后续文章会详细介绍。文章来源地址https://www.toymoban.com/news/detail-496781.html

到了这里,关于【PCIE体系结构三】PCIE的硬件拓扑结构和逻辑层次结构的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!