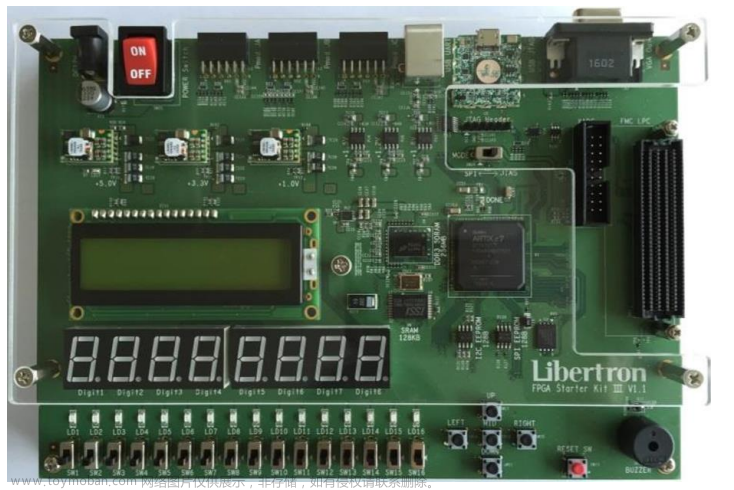

一. 元器件介绍

这里用到的元器件有:

-

DIgital power(VCC)数字电源 -

DIGITAL-CLOCK数字时钟 -

逻辑分析仪(XLA) -

ground数字地 -

SPST单刀单掷开关 -

74HC74D_4VD触发器芯片 -

DCD_HEX数码管(带译码器四位二进制输入) -

PROBE电位探测灯 -

PB_DPST弹簧式触发开关 -

SPDT单刀双掷开关

二. 原理分析

先来说说D触发器的原理:74HC74D_4V D触发器芯片有六个:D输入、Preset输入、Clear输入、

Q

\mathsf{Q}

Q输出、

Q

‾

\overline{\mathsf{Q}}

Q输出、Clock时钟输入

| D | C L K ‾ \overline{\mathsf{CLK}} CLK | Q \mathsf{Q} Q | Q ‾ \overline{\mathsf{Q}} Q |

|---|---|---|---|

| 0 | ↓ | 0 | 1 |

| 1 | ↓ | 1 | 0 |

↓ = clock transition HIGH to LOW

先来纠正一个错误:

图中74HC74D_4V D触发器芯片为下降沿触发

可实际上查阅相关芯片信息,描述为

the 74hc74 are dual posiN/Ave edge triggered d-type flip-flop.

依据74HC74D数据手册(及实验所得结果)

74HC74D数据手册

表示该芯片实际上为上升沿触发,这就是为什么看到逻辑分析仪上的信号跳变为上升沿跳变

实际74HC74D逻辑符号为:

可以看到时钟输入为上升沿触发

据此

| D | CLK | Q \mathsf{Q} Q | Q ‾ \overline{\mathsf{Q}} Q |

|---|---|---|---|

| 0 | ↑ | 0 | 1 |

| 1 | ↑ | 1 | 0 |

↑ = clock transition LOW to HIGH

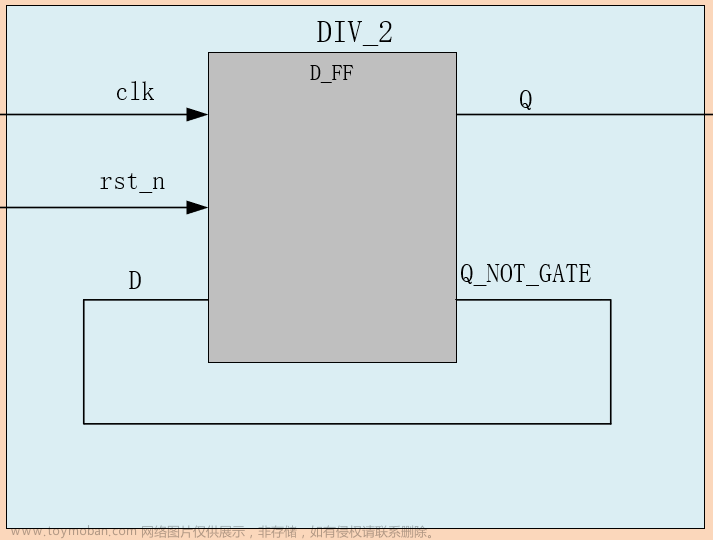

D触发器模拟计数器的原理为:

D触发器翻转输入信号并向下传递

每向下传递一个信号值实现一次二进制的进位

将每一位输出信号输出作为二进制计数值

其结构上和分频器完全一致,不过是同一种电路下实现的两种不同功能

关于D触发器模拟分频器和计数器的异同:

(1)分频器实现的是将输入时钟频率二分频

(2)计数器实现的是将每一个输出信号依输出顺序作为二进制数的低位至高位(或高位至低位)

即:

(1)分频器关注的是时间概念

(2)计数器关注的是输入输出信号

计数器的原理:

- 每当有高电平输入时钟信号端时,依据D触发器

真值表,D触发器 Q ‾ \overline{\mathsf{Q}} Q输出D输入信号的相反值,实现输入信号的翻转,同时将 Q ‾ \overline{\mathsf{Q}} Q输出信号接入到D输入端上,用以实现进位(通过翻转实现二进制的进位,这是D触发器模拟计数器的核心),而输出信号记录为一位二进制数 - 根据D触发器的个数,定义输出二进制数的位数,由D触发器先输出的数值对应为二进制数低位,后输出的数值对应为二进制数的高位

- 当计数到最高位即所有引脚输入都为高电平时,下一刻,输入时钟信号使D触发器输出信号全部翻转为0,回到

初始态,实现循环计数

单个D触发器在模拟计数器的过程中充当进位器

数码管原理:

- DCD_HEX 数码管显示

- SEVEN_SEG 七段数码管显示

本仿真实验使用 DCD_HEX 数码管简化电路

三. 仿真实验

1. 单步触发计数器

需要快速作图的小伙伴直接copy下方图片中的接线即可

以下图实现三位二进制数计数器为例

接线:

- 将

Preset输入、Clear输入同时接入高电平使该引脚失效 - D输入接

Q

‾

\overline{\mathsf{Q}}

Q输出实现沿时钟

上升沿翻转实现数值进位 - 时钟端接入

PB_DPST弹簧式触发开关另一端接到VCC,浮空接地

(注意弹簧式触发按钮必须满足至少有三个引脚接入电路,否则会报错) - 输出

Q

\mathsf{Q}

Q接入数码管

LSB(least significant bit)最低位输入端

如下图实现一位二进制数进位

将两个D触发器组合在一起实现两位二进制输入的一位计数器

注意Q输出按顺序接入数码管引脚

最后将三个D触发器结合在一起实现一个完整的数字由0-7计数的一位计数器

过程分析:

绿灯接入第一个D触发器 || 对应最低位二进制数(LSB)

橙灯接入第二个D触发器 || 对应第二位二进制数

红灯接入第三个D触发器 || 对应最高位二进制数(MSB)

灯亮起代表此线上输出电位为高电平,由此分析输出D触发器实现进位的作用过程

2. 沿时钟计数器

对于沿时钟计数的计数器

同样可以由D触发器模拟

原理不变,将PB_DPST弹簧式触发按键更改为数字时钟信号源

调整合适的输入信号频率

将输出接入逻辑分析仪进行分析

注意设置合适的数字时钟频率以及逻辑分析仪接受频率以显示合适的图像

(该仿真实验中选择数字时钟频率为10HZ,接受时钟频率为20HZ,显示时钟格数为2-4最适)

逻辑分析仪显示如下图

可以发现输出信号和分频器的作用下输出的信号完全一致文章来源:https://www.toymoban.com/news/detail-497298.html

希望能够帮到迷途之中的你,知识有限,如有学术错误请及时指正,感谢大家的阅读文章来源地址https://www.toymoban.com/news/detail-497298.html

(^^)/▽ ▽\(^^)

到了这里,关于Multisim实现D触发器模拟异步计数器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!