前言:

持续更新,若有后续更新,更新链接将附于文末,后续有时间会对内容更新。

课堂tips

1、放大器

放大器放大的是小信号,只有在特定的静态工作点下,小信号放大才有意义,因此一些小信号指标常与某个DC点相关联,若小信号幅度超过系统输入范围要求,则将会发生线性失真,合适的静态工作偏置点是实现信号放大的前提条件。

2、有源器件

有源器件除了PN结,其他至少有三个或以上的端口,是信号可以放大的物理结构前提条件,

3、设置静态工作点Q的原因

有源器件正常工作的条件是需要设置合适的静态工作点,在此前提下,线性近似条件才能成立

4、小信号近似的意义:

①在某个静态工作点Q下,跨导参数gm和gd具有近似常数的性质

②对于输入小信号vgs的放大条件是线性的

5、为什么MOS可以作为放大元件

①从结构上看,MOS管是一个三端口器件,可以视为VCCS/CCCS,栅源极为控制端,DS为受控端,通过调整控制端可对输出进行调整电流大小

②从物理结构上看,作为放大作用,一般工作在饱和区,一般gm>>gd,MOS本征增益Av=gm/gd >>所以MOS有放大功能。

③MOS放大的条件:有固定的静态工作点,且放大的是小信号(线性放大)

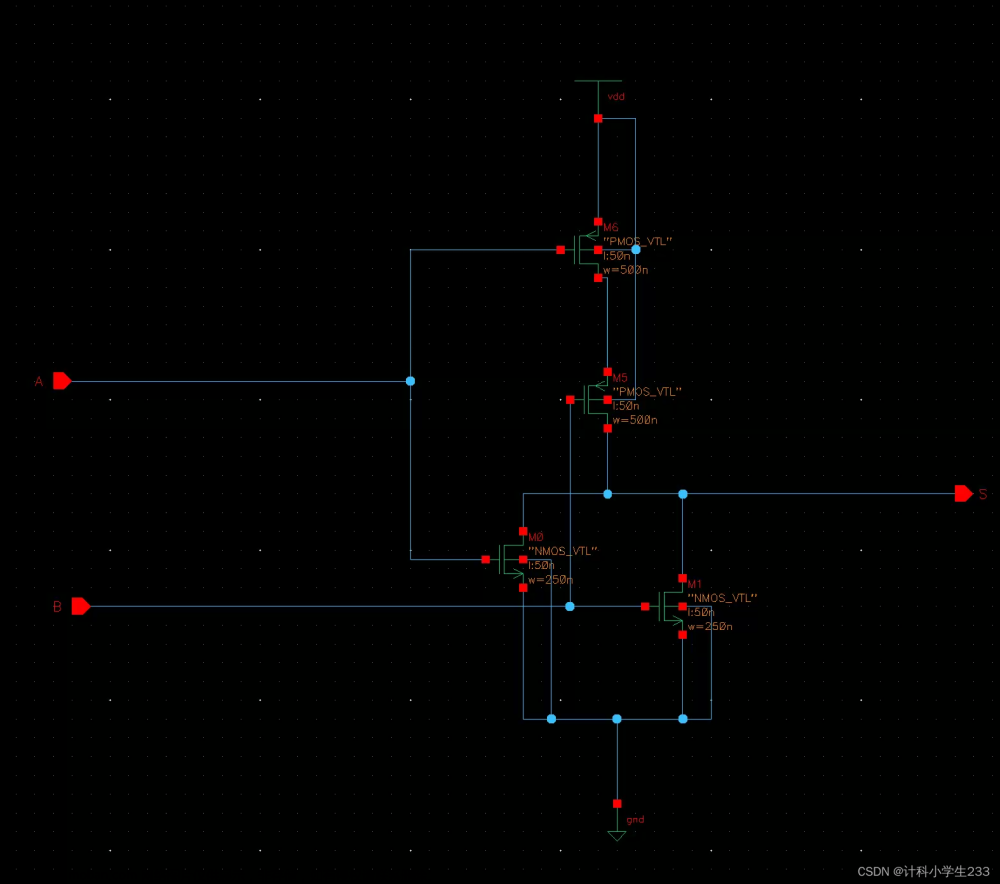

6、集成电路中三种电阻(按照实现方式分类)

①线性电阻:电路简单,交直流阻抗未分离,增益与静态工作点存在矛盾(以经典CS放大器为例,若R过大,MOS进入线性区)。

②恒流源:放大倍数高,交直流分离,交流阻抗高,Av大,直流阻抗下降,静态工作点Q难以确定。

③MOS Diode电阻:静态工作点稳定,输出摆幅受限,交流阻抗低,增益小,直流阻抗大,交直流分离。

7、Miller电容:

①定义:跨接在放大器输入和输出端口的电容,常用作频率补偿;

②问题:Miller电容可能会因前馈而引入RHP零点,该零点若靠近低频,则会减缓幅值下降,使得增益交点外推,相位裕度PM下降,大大减小环路稳定性。

③改进:增加电阻RM与CM串联,将RHP零点外推,甚至变为LHP零点;也可串联一个MOS,切断前馈通路。

④Miller电容有效的前提(以二级运放为例):输出负载电容CL不宜过大,否则放大器电压增益下降,有效增益下降,不能采用低频增益计算Miller效应;Miller效应的目的是将级间极点补偿为主极点,若

C

L

C_{L}

CL太大,输出极点会成为主极点,此时Miller补偿失效;同时第一级输出应为高阻,确保级间极点为主机极点。

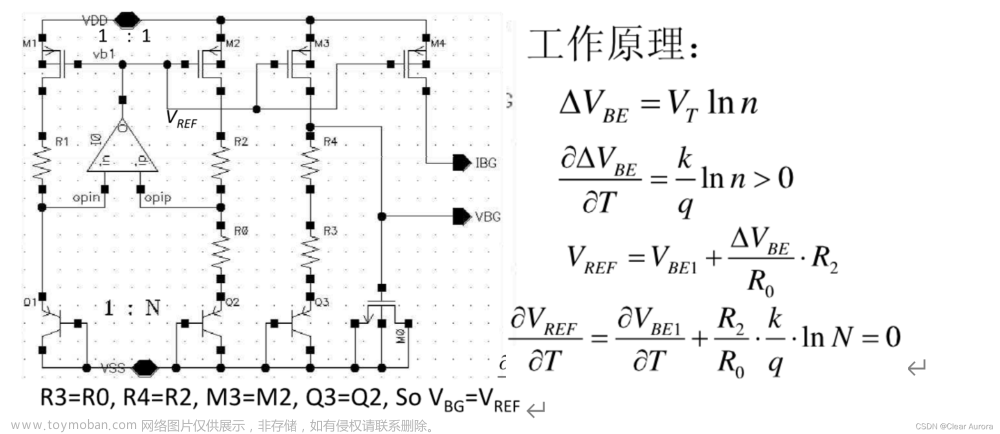

8、Bandgap原理

原理:通过将两个具有相反温度系数的电流或电压通过加权叠加,结果得到零温度系数,双极型晶体管 V B E V_{BE} VBE,PN结二极管的正向电压具有负温度系数, ∆ V B E ∆V_{BE} ∆VBE具有正的温度系数,将 V B E V_{BE} VBE与 ∆ V B E ∆V_{BE} ∆VBE适当增加,可以得到令人满意的零温度系数。

9、MOS管的直流阻抗和交流阻抗

条件:MOS的直流打信号条件下用作直流阻抗,在交流小信号条件下用作交流阻抗

特点:MOS工作在线性区时,直流与交流阻抗近似相等,在饱和区时,交流阻抗远大于直流阻抗,直流阻抗与交流阻抗由MOS静态Q点决定:

交流阻抗

r

d

=

d

V

D

S

/

d

I

D

S

r_{d}=dV _{DS}/dI_{DS}

rd=dVDS/dIDS,主要应用在小信号模型中;直流阻抗

R

d

=

V

D

S

/

I

D

S

R_{d}=V_{DS}/I_{DS}

Rd=VDS/IDS主要应用在大信号模型中。

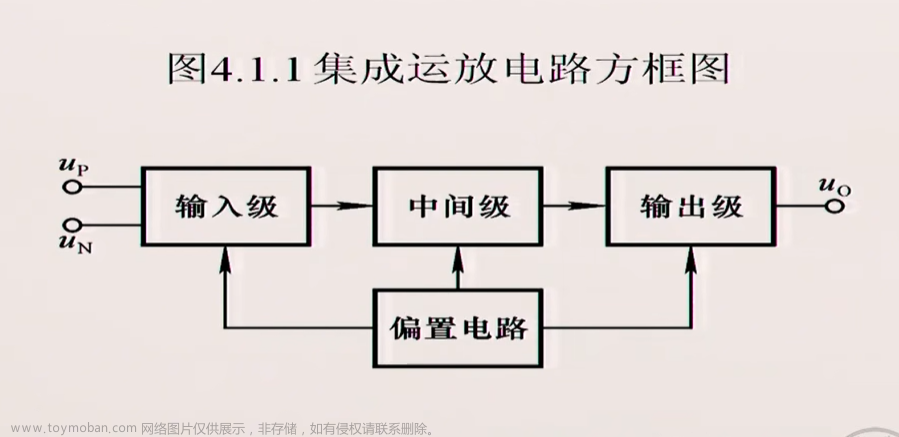

10、运放的开环与闭环

①开环运放:静态点不宜稳定;放大倍数Av不稳定,易受工艺或环境影响;Av不宜灵活改变。

②闭环运放:若

A

v

Av

Av足够大,

A

V

=

A

/

(

1

+

A

F

)

≈

1

/

F

A_{V}=A/(1+AF) \approx 1/F

AV=A/(1+AF)≈1/F。Av近似与开环无关,由反馈系数

F

F

F决定;可以通过F来方便的改变

A

v

Av

Av。

11、零极点的物理意义与形成机制

(1)物理意义:自动控制理论中,极点对应系统瞬态,反映系统响应快慢,与输入无关,是系统本身特性。

(2)形成机制:待我再研究一下

12、MOS和BJT的区别

(1)BJT

①由两种载流子导电,且载流子在半导体内迁移,迁移率大,跨导

g

m

g_{m}

gm大。

②跨导gm大,寄生电容C小,高频性能更好。

③输入有限阻抗,功耗大。

④参数调节与面积S有关,因此器件尺寸较大,不宜集成。

(2)MOS

①由一种载流子导电,且载流子在半导体表面迁移,迁移率小,跨导

g

m

g_{m}

gm小。

②跨导

g

m

g_{m}

gm小,寄生电容C大,高频性能差。

③输入阻抗大,功耗小。

④参数调节与

W

/

L

W/L

W/L有关,因此器件尺寸较小,宜集成。

13、闭环应用

①Av稳定可靠,且通过控制反馈系数F,可编程性提高,应用更灵活。

②-3dB带宽提升,频率特性相应提升,高频性能提升。

③线性范围拓展,线性度提升。

④通过闭环反馈,更易实现阻抗匹配,信号传输损耗小。文章来源:https://www.toymoban.com/news/detail-498498.html

14、差分放大器的优点

①扩大共模输入范围

②有效抑制共模噪声,提高CMRR

③增大输出摆幅(单端输出的两倍)

④偏置电路更简单,差分对通过电流镜直接耦合,输出线性度更高。文章来源地址https://www.toymoban.com/news/detail-498498.html

到了这里,关于【模拟CMOS集成电路设计】学习笔记(一)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!