集成电路以半导体单晶硅为芯片,采用专门的制造工艺,把晶体管、场效应管、二极管、电阻和电容等元件及它们之间的连线所组成的完整电路制作在一起,使之具有特定的功能。集成放大电路最初多用于各种模拟信号的运算(如比例、求和、求差、积分、微分…)上,故被称为运算放大电路,简称集成运放。集成运放广泛用于模拟信号的处理和产生电路之中,因其高性能低价位,在大多数情况下,已经取代了分立元件放大电路。

一、集成运放电路的结构特点

我们知道,在集成电路中,相邻元器件的参数具有良好的一致性;纵向晶体管的

β

\beta

β 大,横向晶体管的耐压高;电阻的阻值和电容的容量均有一定的限制;便于制造互补式 MOS 电路等特点。这些特点使得集成放大电路与分立元件放大电路在结构上有较大的差别。观察它们的电路图可以发现,分立元件放大电路除放大管外,其余元件多为电阻、电容、电感等;而集成放大电路以晶体管和场效应管为主要元件,电阻与电容的数量很少。归纳集成运放的特点如下:

(1)因为硅片上不能制作大电容,所以集成运放均采用直接耦合方式。

(2)因为相邻元件具有良好的对称性,而且受环境温度和干扰等影响后的变化也相同,所以集成运放中大量采用各种差分放大电路(作输入级)和恒流源电路(作偏置电路或有源负载)。

(3)因为制作不同形式的集成电路,只是所用掩膜不同,增加元器件并不增加制造工序,所以集成运放允许采用复杂的电路形式,以达到提高各方面性能的目的。

(4)因为硅片上不宜制作高阻值电阻,所以集成运放中常用有源元件(晶体管或场效应管)取代电阻。

(5)集成晶体管和场效应管因制作工艺不同,性能上有较大差异,所以在集成运放中常采用复合形式,以得到各方面性能俱佳的效果。

二、集成运放电路的组成及其各部分的作用

集成运放电路由输入级、中间级、输出级和偏置电路等四部分组成,如图4.1.1所示。他有两个输入端,一个输出端,图中所标

u

P

u_P

uP、

u

N

u_N

uN、

u

O

u_O

uO 均以“地”为公共端。

1、输入级

输入级又称前置级,它往往是一个双端输入的高性能差分放大电路。一般要求其输入电阻高,差模放大倍数大,抑制共模信号的能力强,静态电流小。输入级的好坏直接影响着集成运放的大多数性能参数,因此,在几代产品的更新过程中,输入级的变化最大。

2、中间级

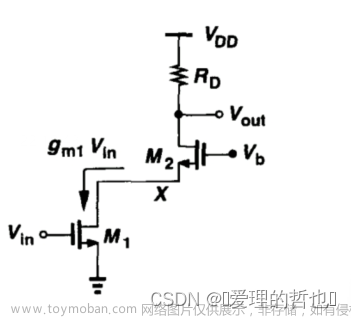

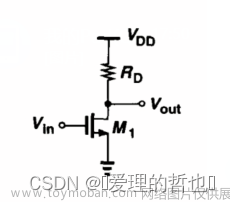

中间级是整个放大电路的主放大器,其作用是使集成运放具有较强的放大能力,多采用共射(或共源)放大电路。而且为了提高电压放大倍数,经常采用复合管作放大管,以恒流源作集电极负载。其电压放大倍数可达千倍以上。

3、输出级

输出级应具有输出电压线性范围宽、输出电阻小(即带负载能力强)、非线性失真小等特点。集成运放的输出级多采用互补输出电路。

4、偏置电路

偏置电路用于设置集成运放各级放大电路的静态工作点。与分立元件不同,集成运放采用电流源电路为各级提供合适的集电极(或发射极、漏极)静态工作电流,从而确定了合适的静态工作点。文章来源:https://www.toymoban.com/news/detail-499657.html

三、集成运放的电压传输特性

集成运放有同相输入端和反相输入端,这里的“同相”和“反相”是指运放的输入电压与输出电压之间的相位关系,其符号如图4.1.2(a)所示。从外部看,可以认为集成运放是一个双端输入、单端输出,具有高差模放大倍数、高输入电阻、低输出电阻、能较好地抑制温漂的差分放大电路。 集成运放的输出电压

u

O

u_O

uO 与输入电压(即同相输入端与反向输入端之间的电位差)(

u

P

−

u

N

u_P-u_N

uP−uN)之间的关系曲线称为电压传输特性,即

u

O

=

f

(

u

P

−

u

N

)

(

4.1.1

)

u_O=f(u_P-u_N)\kern 60pt(4.1.1)

uO=f(uP−uN)(4.1.1)对于正、负两路电源供电的集成运放,电压传输特性如图4.1.2(b)所示。从图示曲线可以看出,集成运放有线性放大区域(称为线性区)和饱和区域(称为非线性区)两部分。在线性区,曲线的斜率为电压放大倍数;在非线性区,输出电压只有两种可能的情况,

+

U

O

M

+U_{OM}

+UOM 或

−

U

O

M

-U_{OM}

−UOM。

集成运放的输出电压

u

O

u_O

uO 与输入电压(即同相输入端与反向输入端之间的电位差)(

u

P

−

u

N

u_P-u_N

uP−uN)之间的关系曲线称为电压传输特性,即

u

O

=

f

(

u

P

−

u

N

)

(

4.1.1

)

u_O=f(u_P-u_N)\kern 60pt(4.1.1)

uO=f(uP−uN)(4.1.1)对于正、负两路电源供电的集成运放,电压传输特性如图4.1.2(b)所示。从图示曲线可以看出,集成运放有线性放大区域(称为线性区)和饱和区域(称为非线性区)两部分。在线性区,曲线的斜率为电压放大倍数;在非线性区,输出电压只有两种可能的情况,

+

U

O

M

+U_{OM}

+UOM 或

−

U

O

M

-U_{OM}

−UOM。

由于集成运放放大的是差模信号,且没有通过外电路引入反馈,故称其电压放大倍数为差模开环放大倍数,记作

A

o

d

A_{od}

Aod,因而当集成运放工作在线性区时

u

O

=

A

o

d

(

u

P

−

u

N

)

(

4.1.2

)

u_O=A_{od}(u_P-u_N)\kern 55pt(4.1.2)

uO=Aod(uP−uN)(4.1.2)通常

A

o

d

A_{od}

Aod 非常高,可达几十万倍,因此集成运放电压传输特性中的线性区非常之窄。如果输出电压的最大值

±

U

O

M

=

±

14

V

±U_{OM}=±14\,\textrm V

±UOM=±14V,

A

o

d

=

5

×

1

0

5

A_{od}=5\times10^5

Aod=5×105,那么只有当

∣

u

P

−

u

N

∣

<

28

μV

|u_P-u_N|<28\,\textrm{μV}

∣uP−uN∣<28μV 时,电路才工作在线性区。换言之,若

∣

u

P

−

u

N

∣

>

28

μV

|u_P-u_N|>28\,\textrm {μV}

∣uP−uN∣>28μV,则集成运放进入非线性区,因而输出电压

u

O

u_O

uO 不是

+

14

V

+14\,\textrm V

+14V,就是

−

14

V

-14\,\textrm V

−14V。文章来源地址https://www.toymoban.com/news/detail-499657.html

到了这里,关于4.1 集成运算放大电路概述的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!