目录

引言

脚本仿真步骤分析

完整的脚本代码

保姆级使用教程

扩展

引言

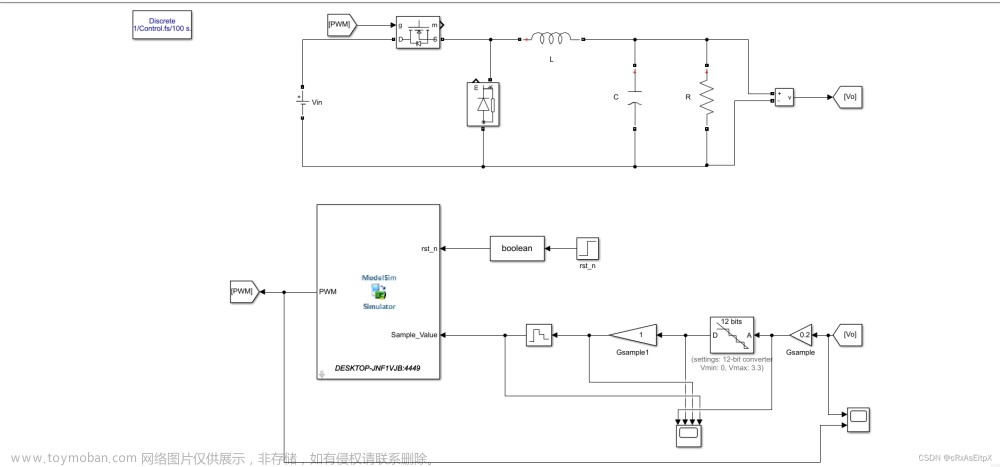

之前对于工程一直采用的是vivado+questasim联合仿真的模式,对于大型工程来说这个是合适的,因为需要调用一些ip库和包括约束之类的,vivado的图形化界面做的很完善,基本是一站式服务了;而对于一个小demo来说,如果为此要新建一个工程的话操作还是有点复杂的,而且占据的空间也很大。并且对于一个合格的工程师来说,最好还是减少重复工作,毕竟已经21世纪了(虽然我还做不到),所以自己就闲的探索了一下基于脚本化的自动仿真流程,只需要有一个设计文件和TB文件即可对一些小demo完成仿真。

脚本仿真步骤分析

本工程的例子为对一个异步fifo的脚本化仿真测试

1、首先我们先创建一个.do文件,方法随意,我一般建一个txt,然后后缀改成.do,例如 auto_test.do

2、此do文件是在Questa/Modelsim的命令行中执行的,所以需要先退出当前工程,命令为:

quit -sim3、然后清除命令行的显示信息

.main clear4、仿真器需要创建一个物理目录(文件夹),将编译后的库文件放在其中,以便仿真的时候对其进行调用

vlib ./lib

vlib ./lib/work5、创建逻辑库(work),并映射逻辑库到物理目录,编译工程之后的编译文件存放在该目录下

vmap work ./lib/work6、编译Verilog 源代码,将编译得到的信息文件与编译的文件放到逻辑库里面,库名缺省编译到work本地库,文件按顺序编译。

主要是编译设计文件,测试文件,调用的IP核.v文件,相应的库文件,通配符./../xxx/ *.v,要注意编译的顺序.

NOTE:测试tb文件放在./tb文件夹下,设计文件放在./source文件夹下

vlog -work work ./tb/*.v

vlog -work work ./source/*.v7、优化部分参数(-voptargs=+acc),链接到默认的work 库,启动仿真顶层测试逻辑库(work)里面的tb文件。

NOTE:这里的测试tb文件名字是tb_asyn_FIFO,使用的时候需要修改为自己tb的名字。

vsim -voptargs=+acc work.tb_asyn_FIFO8、添加波形 add wave 测试顶层的名字/例化子模块的例化名字/子模块信号的名字

add wave -radix bin tb_ex_shift_reg/o_lvds_d

添加分割线:不同的信号之间进行分割,语法格式是

add wave -divider {分割线的名字}

NOTE:可以修改添加wave的方式为从wave.do中读取,wave.do为手动添加波形之后保存的文件

这里直接添TB顶层的所有信号

add wave tb_asyn_FIFO/*9、开始仿真,可以自己设定仿真时间

run 1ms完整的脚本代码

例子为对一个异步fifo的脚本化仿真测试

quit -sim

.main clear

vlib ./lib

vlib ./lib/work

vmap work ./lib/work

vlog -work work ./tb/*.v

vlog -work work ./source/*.v

vsim -voptargs=+acc work.tb_asyn_FIFO

add wave tb_asyn_FIFO/*

run 1ms保姆级使用教程

1、首先创建一个自己的工程文件夹,如asyn_fifo,在里面创建两个文件夹,分别为source和tb,source文件夹存放所有的设计文件,tb文件夹存放所有的tb文件。

2、将脚本do文件和两个文件夹放在同一个目录中,如图所示

3.在questa/modelsim中change directory 到工程文件夹中

4.在命令行中执行do auto_test.do命令

5.之后仿真器便自动开始刷刷刷执行了

扩展

1、如果用到厂商的IP库,在脚本中也是可以添加进去的,但是我做的时候只针对小demo的实现,一般用不上,大家有需要的可以去查阅其他资料。

2、执行后仿之类的操作,仿真器也有相关的指令,这里也不再说明,理由同上。

显示状态机的状态

我们在Modelsim/Questasim中进行仿真的时候,经常会苦恼于状态机的状态跳转不够直观,因为一般状态机的编码都是格雷码或者二进制码。这时候我们可以在modelsim中直接显示状态机的名称而不是数字。

一般用的方法有三种,分别为

- 在testbench文件中对设计文件中的各种状态进行映射

- 在testbench文件中对设计文件中的状态机编码进行重定义

- 使用虚拟对象显示状态机名称

在这里我使用的是第三种,也就是在tcl中进行操作,而不需要修改TB中的内容,对于设计可能会更加方便一些。

virtual type { {2‘b01 ONE} { 2'b10 ZERO} } state_type

virtual function {(state_type)/inst_fsm/state} fsm_state

add wave -color pink /inst_fsm/fsm_state 仿真波形变为

详细的介绍可以参考:在Modelsim仿真中显示状态机名称_kkfeng1002的博客-CSDN博客

参考文献文章来源:https://www.toymoban.com/news/detail-499737.html

基于脚本的modelsim自动化仿真笔记 - IC_learner - 博客园文章来源地址https://www.toymoban.com/news/detail-499737.html

到了这里,关于脚本化Questasim/Modelsim自动仿真——脱离联合仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!