题目:实现图示电路(产生1101001序列码)

详细描述:用VHDL设计194,再用VHDL层次结构设计方法设计程序实现图示电路并仿真,底层器件是194,要求层次化设计,分模块调试

文章来源:https://www.toymoban.com/news/detail-500251.html

二、底层器件

- 194

- 代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY jicunqi IS

PORT(

CR,CP,SL,SR:IN STD_LOGIC;

S0,S1:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q0,Q1,Q2,Q3:out STD_LOGIC

);

END jicunqi;

ARCHITECTURE behavior OF jicunqi IS

signal M1:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CR,CP)

BEGIN

IF CR='0' THEN

M1<="0000";

ELSIF CP'EVENT AND CP ='1' THEN

IF S1='0' AND S0='1' THEN M1<=SR&M1(3 DOWNTO 1);

ELSIF S1='1' AND S0='0' THEN M1<=M1(2 DOWNTO 0)&SL;

ELSIF S1='1' AND S0='1' THEN M1<=D;

END IF;

END IF;

END PROCESS;

Q3<=M1(0);Q2<=M1(1);Q1<=M1(2);Q0<=M1(3);

END BEHAVIOR;- Flow Summary

2.仿真波形及解释

此波形图是验证194的异步清零和并行置数功能

如图 S1和S0置1,D3为高位D0为低位,Q0为低位,Q3为高位。当CP上升沿到达时,Q3Q2Q1Q0的状态开始改变。

当第一个CP上升沿到达时,CR为0,D3D2D1D0为1111,验证同步置数功能,Q3Q2Q1Q0为1111。

第二个CP上升沿到达时,当CR为1时,实现异步清零,Q3Q2Q1Q0为0000,

第三第四第五个CP重复上述操作。

第六个CP上升沿到达时, D3D2D1D0为0001,Q3Q2Q1Q0为0001

同理可得

D3D2D1D0为0010,Q3Q2Q1Q0为0010

D3D2D1D0为1001,Q3Q2Q1Q0为1001

D3D2D1D0为0011,Q3Q2Q1Q0为0011

D3D2D1D0为0110,Q3Q2Q1Q0为0110

D3D2D1D0为0000,Q3Q2Q1Q0为0000

D3D2D1D0为0100,Q3Q2Q1Q0为0100

D3D2D1D0为0111,Q3Q2Q1Q0为0111

此波形图验证194的右移功能S1为0,S0为1,实现右移功能,如上图所示

当S1置0,S0置1,当SR为1时,随着时钟上升沿的到达,SR进入Q0,并在CP的上升沿进行改变,右移1,Q0Q1Q2Q3从0000状态变成1000,1100,1110,1111,

当SR为0时,右移0,Q0Q1Q2Q3从1111依次变为0111,0011,0001,0000,实现了194的右移功能。

此波形图验证194的左移功能S1为1,S0为0,实现左移功能,如上图所示

当S1置1,S0置0,当SR为1时,随着时钟上升沿的到达,SL进入Q3,并在CP的上升沿进行改变,左移1,Q0Q1Q2Q3从0000状态变成0001,0011,0111,1111,

当SR为0时,左移0,Q0Q1Q2Q3从1111依次变为1110,1100,1000,0000,实现了194的左移功能。

如图 当S1S0全置0时,电路保持原状态

- 二输入异或门

- 代码:

Library IEEE;

USE IEEE.std_logic_1164.all;

ENTITY yihuo IS

PORT(a,b:IN std_logic;

c:OUT std_logic);

END yihuo;

ARCHITECTURE behavior of yihuo is

BEGIN c<=(a and not b)or(not a and b);

END ARCHITECTURE behavior;- Flow Summary:

2.波形仿真及解释:

此图验证的是异或的逻辑功能

其中,a与b为输入,c为输出

当a为0,b为1时,输出c为1

当a为1,b为0时,输出c为1

当a为1,b为1时,输出c为0

当a为0,b为0是,输出c为0

满足了c=a⊕b=a·b'+a'·b

- 三输入或非门

(1)代码:

Library IEEE;

USE IEEE.std_logic_1164.all;

ENTITY huofei IS

PORT(a,b,c:IN std_logic;

d:OUT std_logic);

END huofei;

ARCHITECTURE behavior of huofei is

BEGIN d<=not(a or b or c);

END ARCHITECTURE behavior;- Flow Summary:

- 波形仿真及解释:

此图验证的是三输入或非的逻辑功能

其中a,b,c为输入d为输出

由d=not(a+b+c),可以得知当a,b,c中任意一个输入1,其输出都为0,而图中当a、b、c单独为1时,d的输出都为0,当a、b,a、c,b、c,a、b、c都为1时,d也输出0,当且仅当a、b、c都为0时d才输出1。

三、完整电路

- 代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY homework IS

PORT(

CP:IN STD_LOGIC;

Z:out STD_LOGIC

);

END homework;

ARCHITECTURE behavior OF homework IS

COMPONENT JICUNQI

PORT(

CR,CP,SL,SR:IN STD_LOGIC;

S0,S1:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q0,Q1,Q2,Q3:out STD_LOGIC

);

END COMPONENT jicunqi;

COMPONENT YIHUO

PORT(a,b:IN std_logic;

c:OUT std_logic);

END COMPONENT YIHUO;

COMPONENT HUOFEI

PORT(a,b,c:IN std_logic;

d:OUT std_logic);

END COMPONENT HUOFEI;

signal E,F,G,H,J:STD_LOGIC;

BEGIN

U1: jicunqi PORT MAP(Q2=>G,S0=>'1',D=>"1111",CP=>CP,CR=>'1',Q0=>E,Q1=>F,S1=>J,SR=>H,SL=>'1');

U2: yihuo PORT MAP(A=>E,B=>G,C=>H);

U3:huofei PORT MAP(A=>E,B=>F,C=>G,D=>J);

Z<=G;

END BEHAVIOR;- Flow Summary:

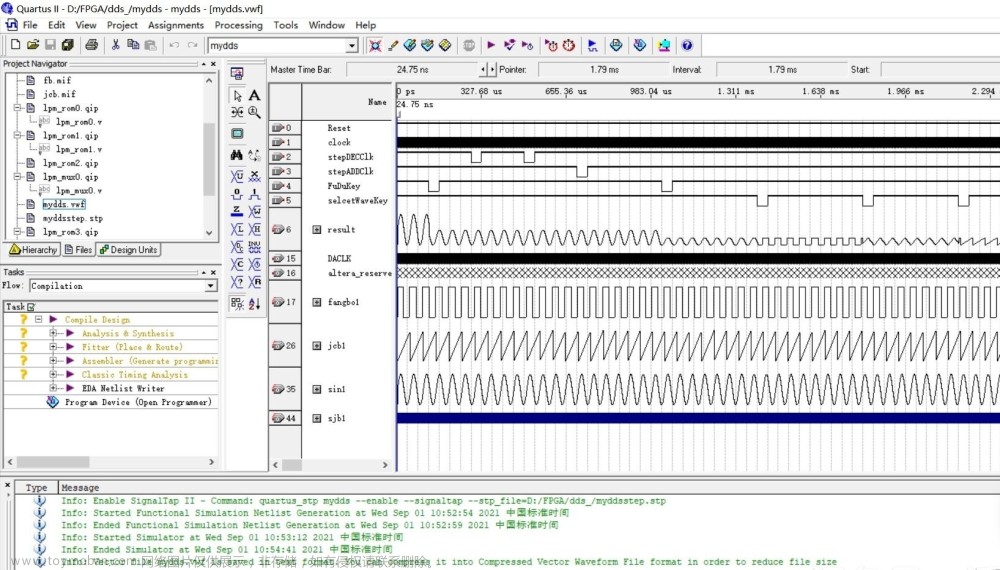

- 波形仿真及其解释:

仿真波形输出截图:

所设计的电路为一个右移的反馈型序列信号发生器,CP为时钟信号,Z为输出

电路的态序表如下:

初始输入状态为1111,当CP上升沿到达时,74LS194开始进行移位操作,电路依次输出1101001文章来源地址https://www.toymoban.com/news/detail-500251.html

到了这里,关于VHDL语言序列信号发生器的实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!