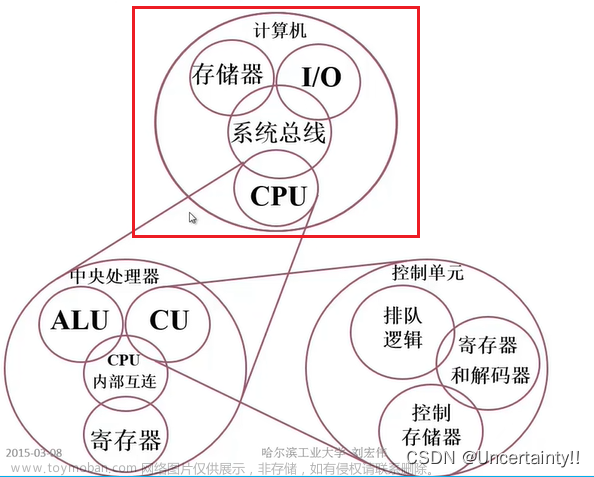

内存

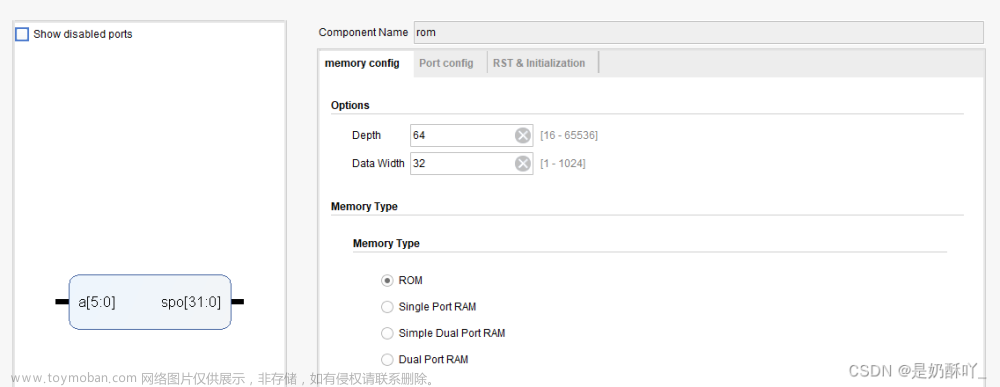

计算机数据存储,存储数据的基本单位是字节(Byte),常说的大b,1字节等于8位,8个bit(小b)。每个字节都对应一个内存地址,内存地址是从0开始编写的,然后自增排列,类似数组,C++当中空类的大小是1个字节,就是为了存储地址。

CPU

32位CPU和64位CPU,这里的位数就是上面的bit位,所以32位CPU一次可以计算(32/8)=4 个字节,64位CPU一次可以计算(64/8)=8个字节。

这里的32位、64位又被称为是CPU的字长(这里有文章说是CPU的位宽),代表的是CPU一次可以计算的量,32位CPU能计算的最大数值是 2^32-1 = 4294967295。

总线

总线分为3种:

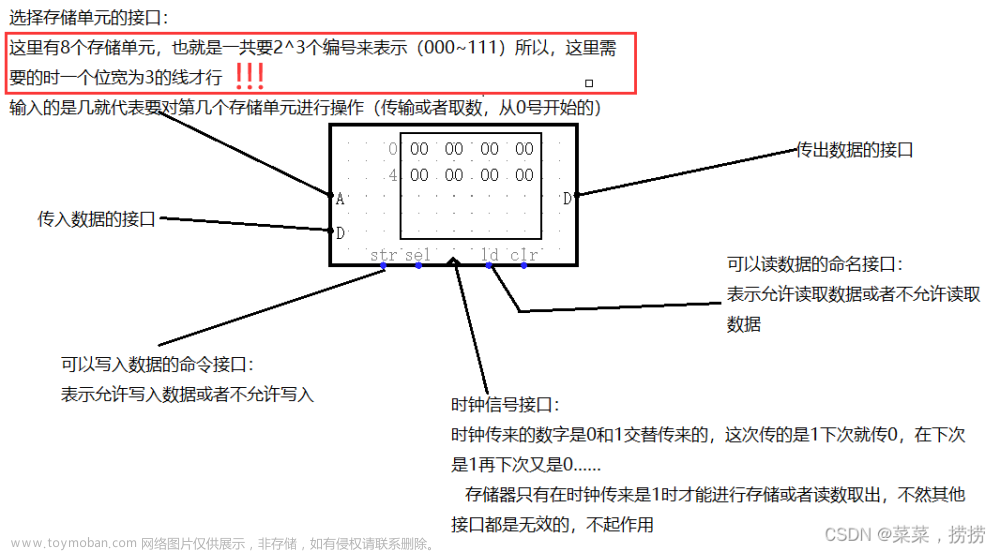

地址总线:用于指定CPU将要操作的内存地址,就是常说的寻址,寻址就依赖于地址总线

数据总线:用于读写内存的数据,CPU位宽指的就是数据总线的位宽

控制总线:用于发送和接收信号如时钟信号、读写控制信号、终端信号等等,这些信号用于控制和同步CPU、内存、输入输出设备等各个组件的操作。

CPU读写内存数据需要哪些动作?

1:通过(地址总线)寻址定位内存的地址

2:通过(控制总线)控制是读还是写指令

3:通过(数据总线)来传输数据

输入输出设备

输入设备和输出设备是计算机系统中用于和外部世界交互的设备。他们分别负责接收外部信息输入和向外部传递信息输出

输入设备:键盘、鼠标、触摸屏、扫描仪、麦克风、摄像头

输出设备:显示器、打印机、喇叭、耳机、投影仪文章来源:https://www.toymoban.com/news/detail-501408.html

CPU位宽和CPU字长

CPU位宽指数据总线的宽度,用于表示和处理二进制数据的位数,它决定了CPU可以同时处理的二进制位数的数量

CPU字长指CPU一次能够处理的二进制位数,CPU字长一般由CPU位宽决定,CPU字长关注的是一次能够处理的数据大小,CPU位宽关注的是寄存器和数据总线的宽度

CPU字长是一个比较老的说法,通常CPU字长和CPU位数是相等的文章来源地址https://www.toymoban.com/news/detail-501408.html

到了这里,关于计算机原理基础一的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!