引言

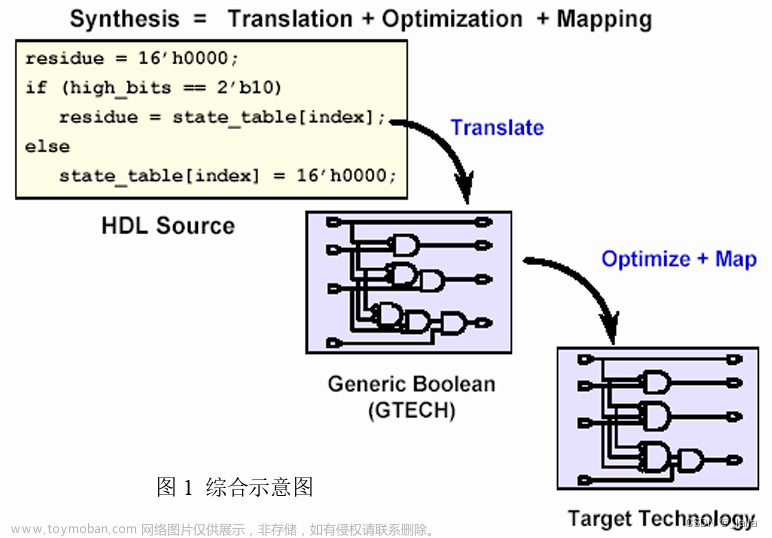

逻辑综合分为三个阶段:

- 转译(Translation):把电路转换为EDA内部数据库,这个数据库跟工艺库是独立无关的;

- 优化(Optimozation):根据工作频率、面积、功耗来对电路优化,来推断出满足设计指标要求的门级网表;

- 映射(Mapping):将门级网表映射到晶圆厂给定的工艺库上,最终形成该工艺库对应的门级网表。

在综合的时候,首先 DC 的 HDL compiler 把 HDL 代码转化成 DC 自带的 GTECH 格式,然后 DC 的library compiler 根据标准设计约束(SDC)文件、IP-DW 库、工艺库、图形库、(使用拓扑模式时,还要加入 ICC 生成的 DEF 模式,加载物理布局信息)进行时序优化、数据通路优化、功耗优化(DC 的 power compiler 进行)、测试的综合优化(DC 的 DFT compiler),最后得到优化后的网表。

关键词:DC综合 综合约束 时序报告

概述

使用DC逻辑综合的流程大致可以分为以下几个部分:

- 预综合过程(Pre-Synthesis Processes):在综合过程之前的一些为综合做准备的步骤:

- DC启动;

- 设置各种库文件:

• link_library;

• target_library;

• symbol_library; - 创建启动脚本文件;

- 读入设计文件;

• analyze;

• elaborate;

• read_file; - DC中的设计对象;

- 各种模块划分;

- Verilog的编码。

- 施加设计约束:

- 设置环境约束:

• set_operating_coditions;

• set_wire_load;

• set_drive;

• set_driving_cell;

• set_load;

• set_fanout_load; - 设置时序约束:

- 设计规则的约束:

• set_max_transition;

• set_max_fanout;

• set_max_capacitance; - 优化的约束:

• create_clock;

• set_clock_skew;

• set_input_delay;

• set_output_delay;

• set_max_area;

- 设计规则的约束:

- 设置环境约束:

- 选择编译策略:

- top down;

- bottom up;

- 设计综合;

- 查看报告;

- 存储设计数据。

读入设计文件

DC提供了两种命令来读入设计:read 命令和 analyze/elaborate 命令。Synopsys 最初引进了read 命令,随后又有了 analyze/elaborate 命令。较之 read 命令,analyze/elaborate 命令为设计输入提供了一种快速而强有力的方法,因此,推荐 RTL 设计输入使用。

DC 的 read 指令支持多种硬件描述格式,不同模式下读取不同格式文件有以下区别:文章来源:https://www.toymoban.com/news/detail-501490.html

- dc_shell工作模式:读取不同的文件格式只需要带上不同的参数:

shell read -format verilog[db、vhdl etc.] file - tcl工作模式:读取不同的文件格式需要使用不同的命令:

shell read_db file.db read_verilog file.v read_vhdl file.vhd

同时使用 analyze 和 elaborate 指令:文章来源地址https://www.toymoban.com/news/detail-501490.html

- analyze:分析 HDL 的源程序并将分析产生的中间文件存于 work(或用户指定)的目录下;

shell analyze -form

到了这里,关于DC综合流程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!