一、&与&&的区别

&&是逻辑与:即判断&&两侧的表达式是否都为真,都为真则此&&表达式值为真;逻辑与结果只讲真和假

& 是按位与:即将&两侧的数用二进制展开,每一位都求与运算(二进制与运算,跟逻辑与差不多),最后得到的二进制数即为结果;按位与得出的却是实实在在的一个数

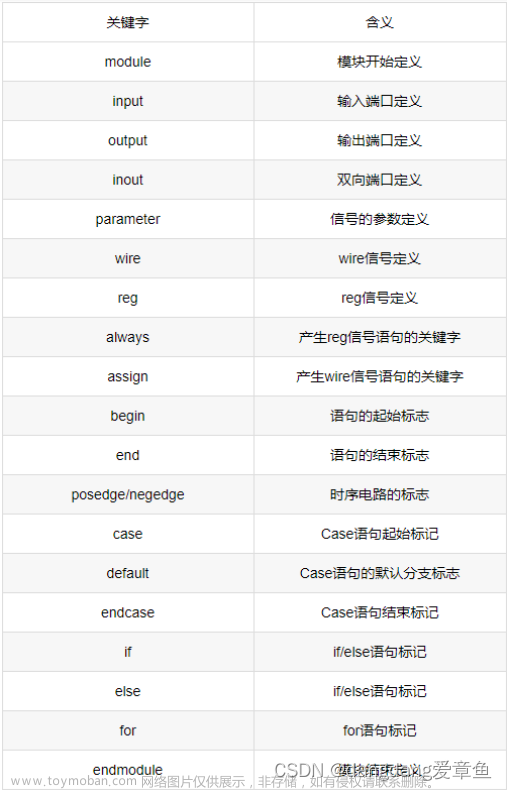

二、位运算符号

~:表示非;

&:表示与;

|:表示或;

^:表示异或 //两者相同则为0,不相等为1

^~:表示同或

三、位移算法

根据移位运算,左移1位相当于×2,右移1位相当于/2

四、数据延时的方法

1、通过打拍延时

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

in<='b0;

tmp1<='b0;

tmp2<='b0;

end

else begin

tmp1<=in;

tmp2<=tmp1;

end

end

2、通过位拼接延时

另外还涉及到流水线时序调整的问题,由于RGB到Ycbcr的转换是进行图像数据的处理,并最终显示在显示屏上,因此显示要与数据的输出同步,由于计算转换后得到的输出数据花费了三个clk。那么对于显示驱动来说,其中的数据使能信号,行同步信号和帧同步信号应该延迟三个clk,才能保证输出数据的正确接收,因此延迟如下:文章来源:https://www.toymoban.com/news/detail-502950.html

//信号同步,保证输出显示可正确接收到数据

//RGB_de,RGB_hsync,RGB_vsync为原本的数据使能信号,行同步信号和帧同步信号

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

RGB_de_r <= 3'b0;

RGB_hsync_r <= 3'b0;

RGB_vsync_r <= 3'b0;

end

else begin //三个clk的延迟操作

RGB_de_r <= {RGB_de_r[1:0], RGB_de};

RGB_hsync_r <= {RGB_hsync_r[1:0], RGB_hsync};

RGB_vsync_r <= {RGB_vsync_r[1:0], RGB_vsync};

end

end

//延迟三个clk的的数据使能信号,行同步信号和帧同步信号

assign gray_de = RGB_de_r[2];

assign gray_hsync = RGB_hsync_r[2];

assign gray_vsync = RGB_vsync_r[2];

参考:https://blog.csdn.net/H19981118/article/details/123970832文章来源地址https://www.toymoban.com/news/detail-502950.html

到了这里,关于verilog易混淆知识点的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[SVA知识点二]: System verilog 断言(assert)的基本介绍](https://imgs.yssmx.com/Uploads/2024/02/788526-1.png)

![[SVA知识点一]: System verilog 断言(assert)的基本介绍](https://imgs.yssmx.com/Uploads/2024/02/692310-1.png)