软件环境

Quartus II+ModelSiml

1bit全加器

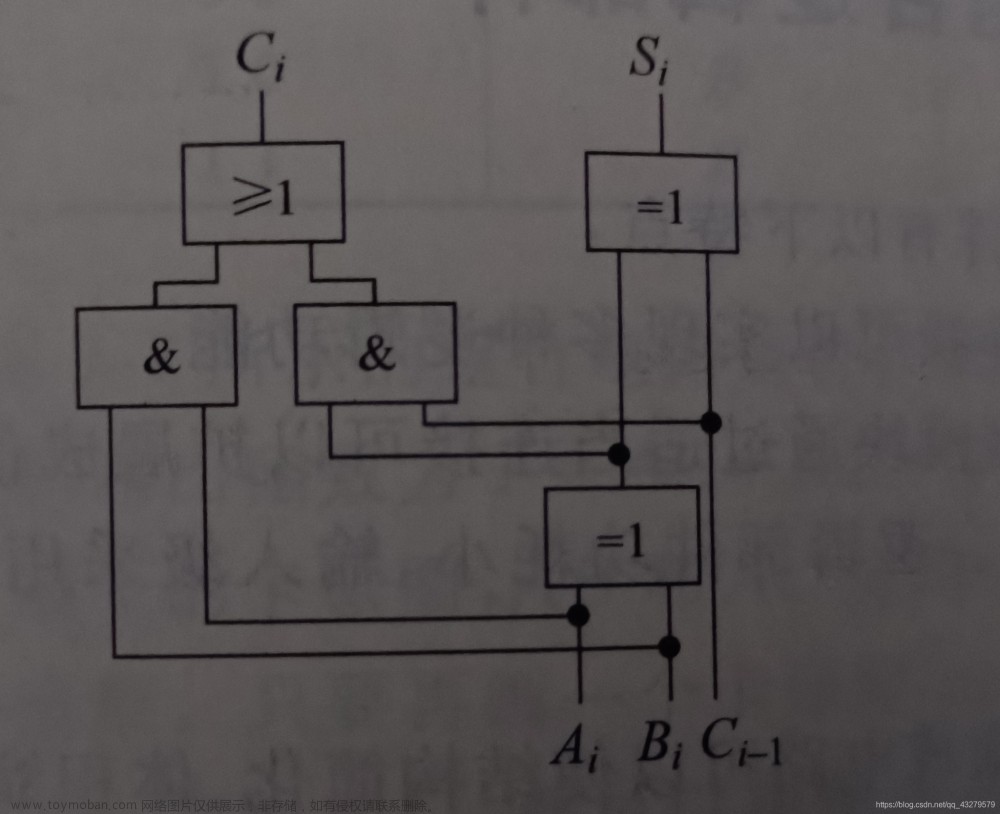

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。

真值表

文章来源:https://www.toymoban.com/news/detail-504384.html

文章来源:https://www.toymoban.com/news/detail-504384.html

Verilog代码

// 注释

// 模块化

module full_adder1(

// input和output均为端口

// Ai,Bi,Ci为输入,So,Co为输出

input Ai, Bi, Ci,

output So, Co);

`ifdef ADDER_DESCRIPTION

// assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量

assign {Co, So} = Ai + Bi + Ci ;

`else

assign So = Ai ^ Bi ^ Ci ;

assign Co = (Ai & Bi) | (Ci & (Ai | Bi));

`endif

endmodule

SystemVerilog代码

`timescale 1ns/1ns

module test ;

reg Ai, Bi, Ci ;

wire So, Co ;

initial begin

{Ai, Bi, Ci} = 3'b0;

forever begin

//if ({Ai, Bi, Ci} == 3'h7)

// $finish ;

#10 ;

{Ai, Bi, Ci} = {Ai, Bi, Ci} + 1'b1;

end

end

full_adder1 u_adder(

.Ai (Ai),

.Bi (Bi),

.Ci (Ci),

.So (So),

.Co (Co));

initial begin

forever begin

#100;

//$display("---gyc---%d", $time);

if ($time >= 1000) begin

$finish ;

end

end

end

endmodule // test

仿真波形

文章来源地址https://www.toymoban.com/news/detail-504384.html

文章来源地址https://www.toymoban.com/news/detail-504384.html

到了这里,关于用Verilog编写1位全加器,并进行波形仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!