Xilinx使用Microblaze软核进行功能开发时,需要将Vivado生成的硬件bit文件和Vitis生成的软件elf文件进行合并,生成软硬结合的bit文件,然后可以选择将该bit文件烧进FPGA、或者将该bit文件转换成mcs文件/bin文件然后烧录至Flash中。

目前使用到了两种合并Vivado bit文件和Vitis elf文件的方法,两种方法亲测均有效:

1、使用Vivado进行合并

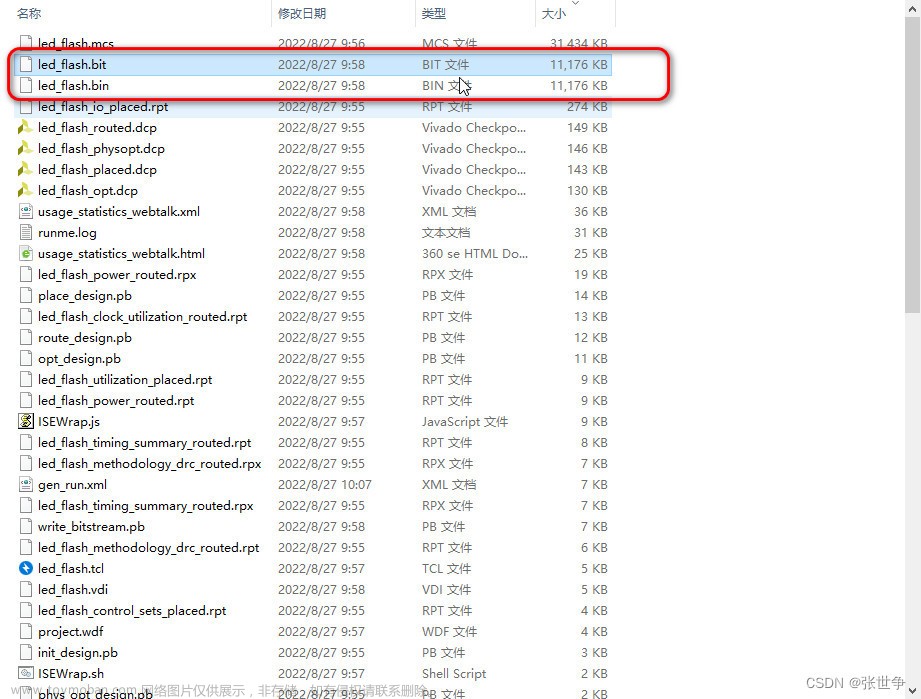

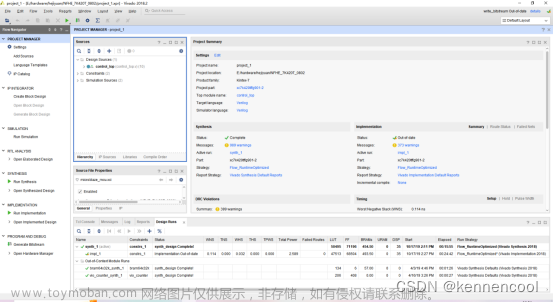

(1)Vivado工程Run Sythesis —> Run Implementation —> Generate Bitsteam正常走完,生成硬件bit文件。

(2)导入vitis工程编译完成后生成的elf文件

(3)点击Generate Bitstream,生成软硬结合的bit文件。此时由于在第1步中,已经完成工程的编译,所以此步并不会导致重新编译工程,只需要等待新的bit文件生成即可。

2、使用Vitis进行合并

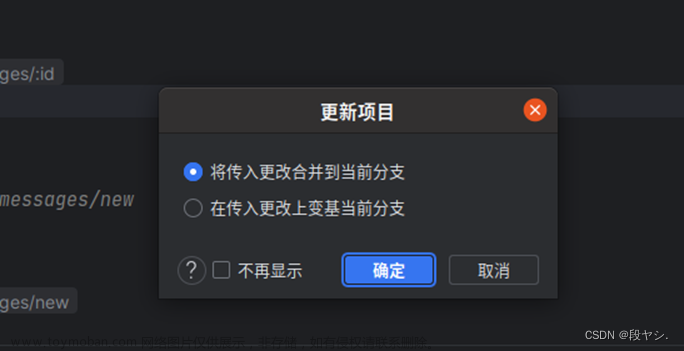

已经编译好的Vitis工程中,点击Xilinx —> Program FPGA —> 选中elf的路径 —> 点击Generate,等待软硬结合的bit文件生成,默认路径在vitis工程的“_ide”文件夹下的“bitstream”文件夹中。

文章来源:https://www.toymoban.com/news/detail-504728.html

文章来源:https://www.toymoban.com/news/detail-504728.html

文章来源地址https://www.toymoban.com/news/detail-504728.html

文章来源地址https://www.toymoban.com/news/detail-504728.html

到了这里,关于Xilinx Vivado bit文件和Microblaze elf文件合并的两种方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!