简介

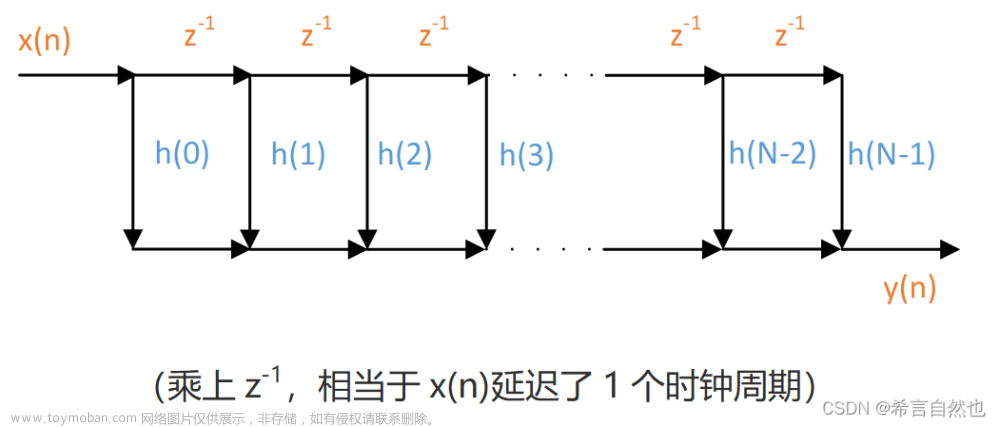

FIR滤波器是非递归型滤波器的简称,又叫有限长单位冲激响应滤波器。带有常系数的FIR滤波器是一种LTI(线性时不变)数字滤波器。冲激响应是有限的意味着在滤波器中没有发反馈。长度为N的FIR输出对应于输入时间序列x(n)的关系由一种有限卷积和的形式给出,具体形式如下:

y

(

n

)

=

Σ

k

=

0

N

−

1

h

(

k

)

×

x

(

n

−

k

)

y(n)=\Sigma_{k=0}^{N-1}h(k)\times x(n-k)

y(n)=Σk=0N−1h(k)×x(n−k)

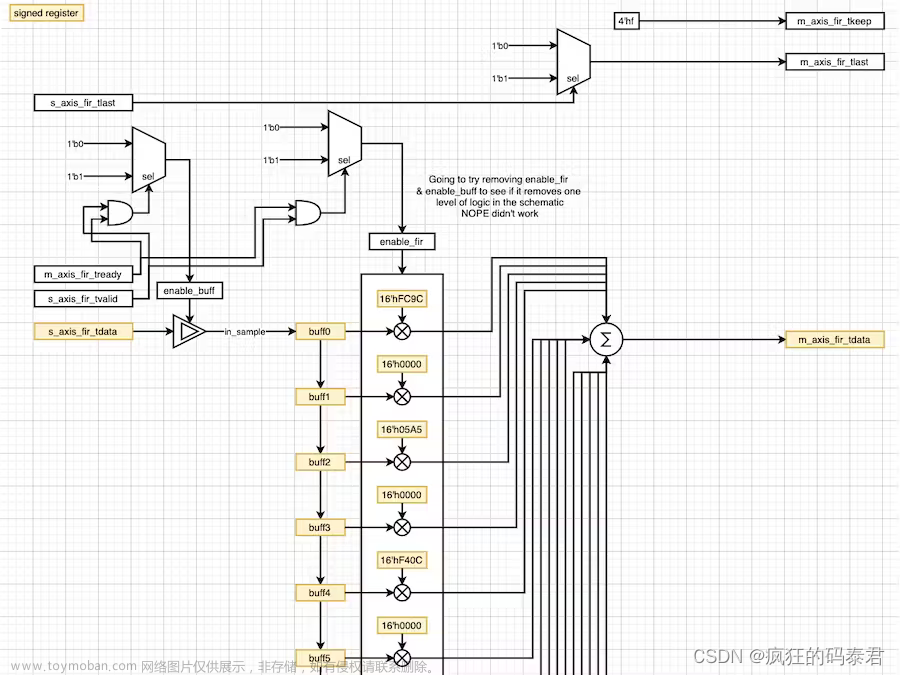

其运算过程可以采用如下图所示的流程:

代码

设计部分(采用移位寄存器+并行乘法阵列+加法树实现)

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/12 14:23:22

// Design Name:

// Module Name: my_fir

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module my_fir

#(parameter F=10)

(

input logic clk,

input logic rst,

input logic signed [15:0] filter_in,

output logic signed [31:0] filter_out

);

//

logic signed [15:0] shift_regs [0:16];

logic signed [15:0] coes [0:16];

logic signed [31:0] mults [0:16];

logic signed [31:0] psum [0:4-1];

logic signed [31:0] sum;

//shift_regs

always@(posedge clk,posedge rst)

if(rst)

for(int i=0;i<=16;i++)

shift_regs[i]<=0;

else

begin

shift_regs[0]<=filter_in;

for(int i=0;i<16;i++)

shift_regs[i+1]<=shift_regs[i];

end

//coes

assign coes[0]=-17;

assign coes[1]=62;

assign coes[2]=456;

assign coes[3]=1482;

assign coes[4]=3367;

assign coes[5]=6013;

assign coes[6]=8880;

assign coes[7]=11129;

assign coes[8]=11983;

assign coes[9]=11129;

assign coes[10]=8880;

assign coes[11]=6013;

assign coes[12]=3367;

assign coes[13]=1482;

assign coes[14]=456;

assign coes[15]=62;

assign coes[16]=-17;

//mults

always@(posedge clk,posedge rst)

if(rst)

for(int i=0;i<=16;i++)

mults[i]<=0;

else

begin

for(int i=0;i<=16;i++)

mults[i]<=coes[i]*shift_regs[i];

end

//psum

always@(posedge clk,posedge rst)

if(rst)

for(int i=0;i<4;i++)

psum[i]<=0;

else

for(int i=0;i<4;i++)

psum[i]<=mults[4*i]+mults[4*i+1]+mults[4*i+2]+mults[4*i+3];

//sum

always@(posedge clk,posedge rst)

if(rst)

sum<=0;

else

sum<=psum[0]+psum[1]+psum[2]+psum[3]+mults[16];

//

assign filter_out=(sum>>>F);

endmodule

测试平台文章来源:https://www.toymoban.com/news/detail-504785.html

`timescale 1ns / 1ps

// Company:

// Engineer: anxu chan

//

// Create Date: 16:17:14 08/02/2017

// Design Name: FIR filter

// Module Name: fir

// Project Name: FirDesign

// Target Devices: Xilinix V5

// Description: test bench

// Revision: 1.0

// Revision 0.01 - File Created

// Additional Comments:

//

module fir_tb;

// Inputs

reg clk;

reg rst;

reg signed [15:0] filter_in;

// Outputs

wire signed [31:0] filter_out;

// Instantiate the Unit Under Test (UUT)

my_fir uut (

.clk(clk),

.rst(rst),

.filter_in(filter_in),

.filter_out(filter_out)

);

// define reset time

initial begin

rst = 1;

#15;

rst = 0;

end

// define clock

initial begin

clk = 0;

forever #10 clk = ~clk;

end

// define a ram store input signal

reg signed[15:0] mem[241:0];

// read data from disk

initial begin

$readmemb("E:\\rtl_project\\fir\\src\\project\\databin.mem" , mem);

end

// send data to filter

integer i=0;

initial begin

#15;

for(i = 0 ; i < 242 ; i = i+1) begin

filter_in = mem[i];

#20;

end

end

// write data to txt File

integer file;

integer cnt=0;

initial begin

file = $fopen("dataout1.txt" , "w");

end

// write data was filtered by fir to txt file

always @(posedge clk) begin

$fdisplay(file , filter_out);

end

always @(posedge clk) begin

$display("data out (%d)------> : %d ," , cnt, filter_out);

cnt = cnt + 1;

if (cnt == 250) begin

#20 $fclose(file);

rst = 0;

#20 $stop;

end

end

endmodule

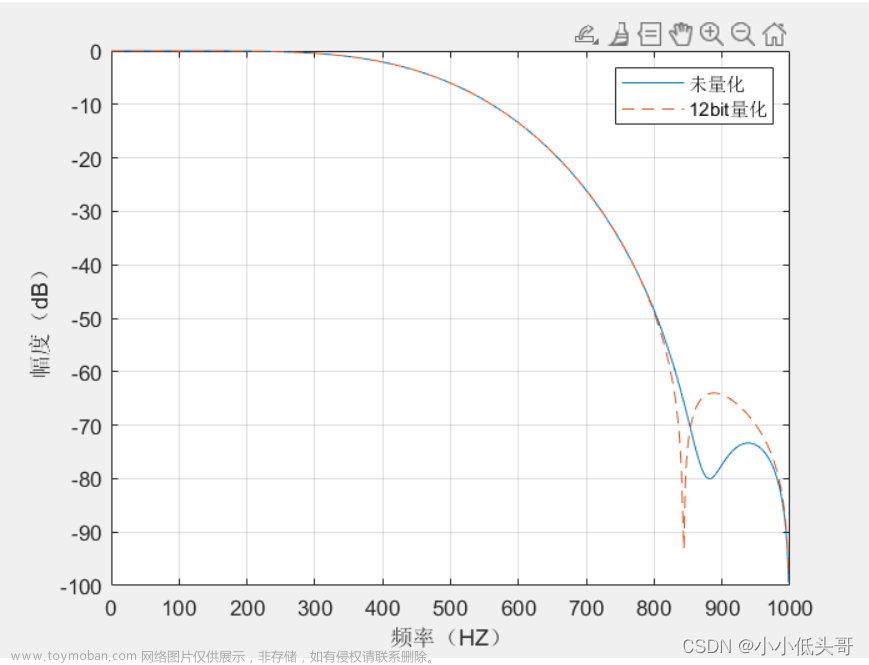

结果

完整工程见链接文章来源地址https://www.toymoban.com/news/detail-504785.html

到了这里,关于FIR滤波器的Verilog实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!