latch 是指锁存器,是一种对脉冲电平敏感的存储单元电路。锁存器和寄存器都是基本存储单元,锁存器是电平触发的存储器,寄存器是边沿触发的存储器。两者的基本功能是一样的,都可以存储数据。锁存器是组合逻辑产生的,而寄存器是在时序电路中使用,由时钟触发产生的。

latch 的主要危害是会产生毛刺(glitch),这种毛刺对下一级电路是很危险的。并且其隐蔽性很强,不易查出。因此,在设计中,应尽量避免 latch 的使用。

代码里面出现latch 的两个原因是在组合逻辑中,if 或者case 语句不完整的描述,比如if 缺少else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。解决办法就是if 必须带else 分支,case 必须带default 分支。

大家需要注意下,只有不带时钟的always 语句if 或者 case 语句不完整才会产生 latch,带时钟的语句if或者 case 语句不完整描述不会产生 latch。

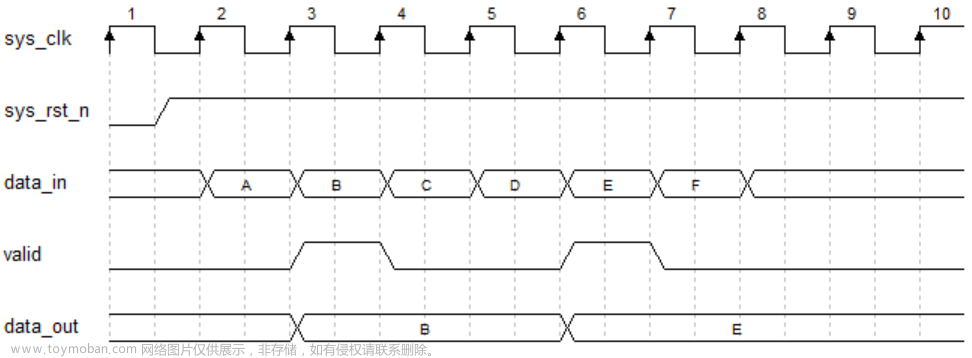

下面为缺少else 分支的带时钟的always 语句和不带时钟的 always 语句,通过实际产生的电路图可以看到第二个是有一个latch的,第一个仍然是普通的带有时钟的寄存器。

文章来源:https://www.toymoban.com/news/detail-505228.html

文章来源:https://www.toymoban.com/news/detail-505228.html

文章来源地址https://www.toymoban.com/news/detail-505228.html

文章来源地址https://www.toymoban.com/news/detail-505228.html

到了这里,关于FPGA之锁存器(Latch)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!