目录

概要

整体架构流程

技术名词解释

技术细节

1.物理层

小结

概要

随着高速ADC跨入GSPS范围,与FPGA(定制ASIC)进行数据传输的首选接口协JESD204B。为了捕捉频率范围更高的RF频谱,需要宽带RFADC。在其推动下,对于能够捕捉更宽带宽并支持配置更灵活的SDR〈软件定义无线电)平台的 GSPSADC。

本文主要介绍JESD204B协议、JESD204B标准是一种分层规范.了解这一点很重要。规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。

整体架构流程

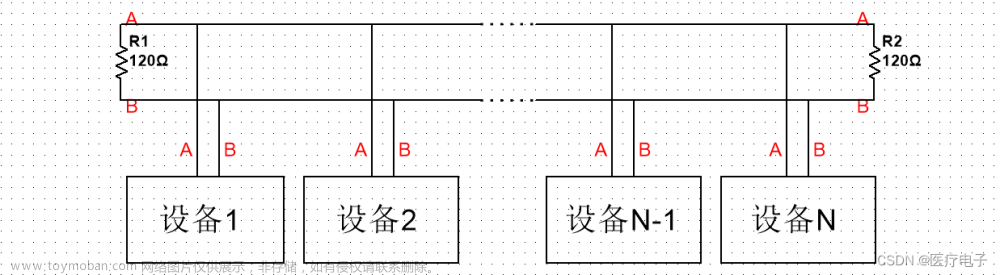

高速串行接口〈在此情况下即JESD204B)是必不可少的。JESD204B标准是一种分层规范.了解这一点很重要。规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。传输层实现转换样本与成帧未加扰八位字之间的映射。

加扰层可以选择性地获取八位字并进行加扰或解扰.以便通过延展频谱尖峰来降低EMI效应。加扰在发送器中完成.解扰在接收器中完成。在数据链路层中,可选加扰的八位字编码成10位字符。该层也是产生或检测控制字符的地方,目的是监视和维护通道对齐。物理层即串行器/解串器〈SERDES)层,负责以线路速率发送或接收字符。

该层包括串行器、驱动器、接收器.时钟和数据恢复电路。图1显示了这些层在JESD204B中的安排。为了更好地理解该规范,详细阐释各层对了解ADC样本如何映射到8B/10B串行字是有好处的。

技术名词解释

提示:这里可以添加技术名词解释

ADC:

模拟数字转换器即A/D转换器,或简称ADC,通常是指一个将模拟信号转变为数字信号的电子元件。通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小 [1] 。

GSPS:

积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属中速AD,全并行/串并行型AD可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换的正确完成,采样速率(Sample Rate)必须小于或等于转换速率。因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。常用单位是ksps和Msps,表示每秒采样千/百万次(kilo / Million Samples per Second)。

在高速数据通信领域,经常使用GSPS(Gigabit Samples Per Second,即每秒千兆次采样)作为单位,1GSPS=1000MSPS=1000,000KSPS.

技术细节

提示:这里可以添加技术细节

1.物理层

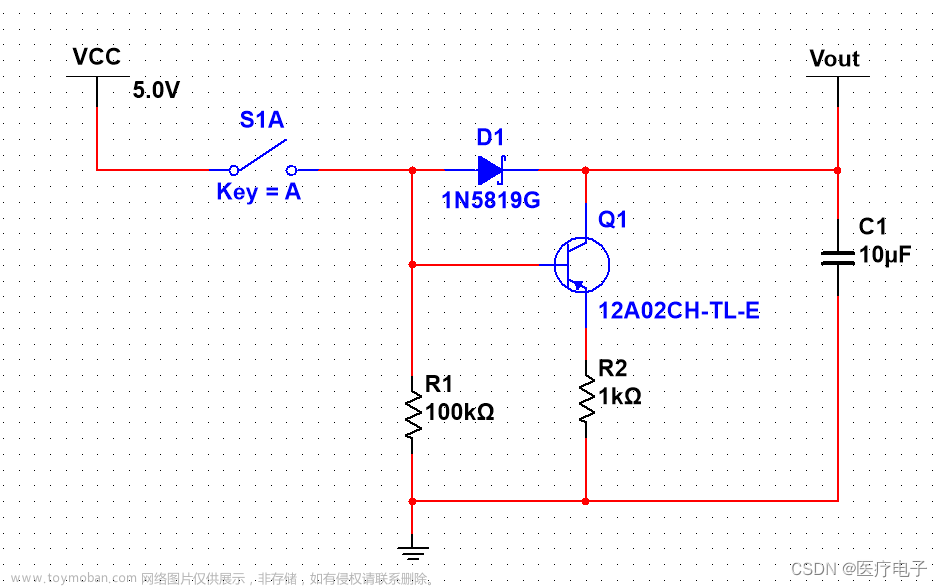

在物理层中.数据进行串行化.8B/10B编码数据以线路速率发送和接收。物理层包括串行/解串器〈SERDES)模块.驱动器、接收器和CDR。由于数据传输速率非常高,这些模块常常采用定制单元设计。JESD204和JESD204A均支持最高3.125Gbps的速度。JESD204B规范支持三种可能的速度等级。速度等级1支持最高3.125Gbps的速度.基于OIF-Sxl5-0.10规范。速度等级⒉支持最高6.375Gbps的速度,基于CEI-6G-SR规范。速度等级3支持最高12.5Gbps的速度.基于CEI-11G-SR规范。表2概要显示了三种速度等级对应的一些物理层规格。

表列出了各种速度等级的JESD204B标准物理层信号的线路速率、差分电压、上升/下降时间和总抖动。速度等级越高,信号幅度越小.保持高压摆率就越容易.因而能够维持开数据眼以正确传输信号。这些高速信号具有快速上升沿和下降沿.对电路板设计的约束非常严格。对于许多宽带RF系统设计者来说,这不是新鲜事。然而.高速数字设计的一个重要区别是宽带宽。典型RF系统的信号带宽约为RF工作频率的10%或以下。对于这些高速串行通道速率.系统设计需要考虑的带宽通常为通道速率的3倍至5倍。通道速率为5Gbps时,信号带宽将是7.5GHz到12.5GHz。对于如此宽的带宽.保持适当的信号完整度并且了解如何衡量信号完整度是很重要的。

在串行差分接口中,眼图是信号完整度的常用测量方法。图5显示了以最高3.125Gbps的速度工作时JESD204发送器的眼图罩。表3提供了有关时序、电压电平.阻抗和回波损耗的详细信息。信号不得侵占图中的米色区域.必须始终处于白色区域中。表中给出了发送器必须满足眼罩的条件。对JESD204B规范中的另外两种速度等级.也有类似的眼图罩。详情请参阅CEI-6G-SR和CEI-11G-SR物理层规范。

小结

提示:这里可以添加总结文章来源:https://www.toymoban.com/news/detail-506167.html

采用JESD204B的设计数量与日俱增.并且涉及诸多市场,例如通信.仪器仪表.军工和航空航天。这些市场推动宽带RF系统设计使用GSPSADC,因而需要JESD204B串行接口。收发器支持JESD204B串行化/解串的FPGA 越来越多,而且越来越便宜。随着JESD204B接口变得越来越受欢迎,了解JESD204B规范的各层是很重要的。如上所述,规范中的各层都有自己的功能要完成。配置和数据映射是应用层的功能.而转换样本与未加扰八位字之间的映射是在传输层完成。加扰可以选择性使能.以通过延展频谱尖峰来降低EMI影响。在数据链路层.可选加扰的八位字编码为8B/10B字符.控制字符的产生或检测也在这里完成.以便支持通道对齐监控和维护。驱动器.接收器.时钟和数据恢复电路构成发送和接收数据的物理层。通过本文,系统设计者应当能够更好地了解JESD204B规范的各层,从而在下一个设计中更加有准备地实施JESD204B。文章来源地址https://www.toymoban.com/news/detail-506167.html

到了这里,关于高速电路设计系列分享-熟悉JESD204B(下)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!