实验:补码生成电路

设计要求:

1、掌握全加器的使用。

2、设计一个8位补码生成电路(包括符号位)。

3、要求用MULTISIMS设计电路并仿真。

涉及芯片:

74LS283D

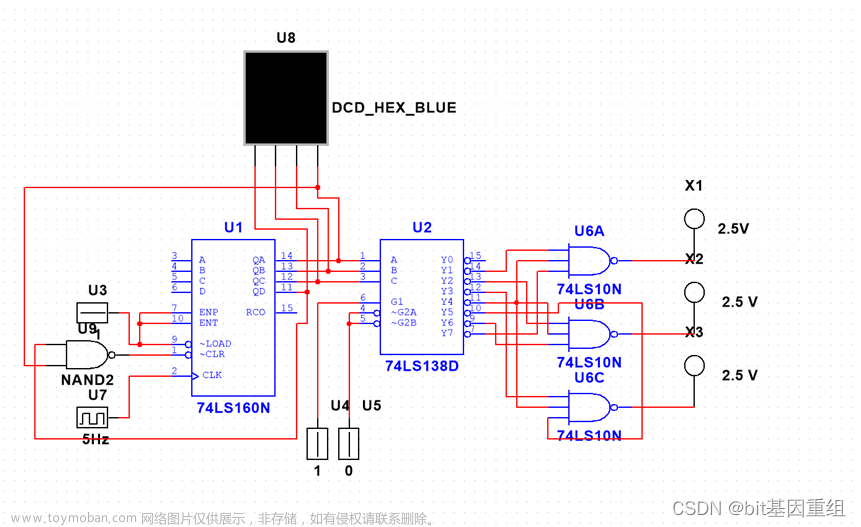

原理图:

此电路可通过八个控制开关进行输入原码,其中S1控制符号位,向右位次逐渐降低

上方八个显示器显示各位原码

下方八个显示器显示各位补码文章来源:https://www.toymoban.com/news/detail-507085.html

源文件: https://www.chongya.com/update/4262b47eac1a4df2a6b39d71eff5b069文章来源地址https://www.toymoban.com/news/detail-507085.html

到了这里,关于8位补码生成电路的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!