实验一: 3-8译码器(原理图输⼊设计)

2.1设计输⼊

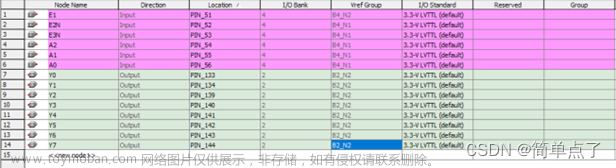

1. 将3-8译码器A、B、C端作为输⼊,Y作为输出。

2. 其余引脚按照3-8译码器功能要求连接。

2.2电路仿真

1. 激励⽂件的输⼊包含A、B、C的8种状态

2. 功能仿真

1. 给出3-8译码器的真值表:

2. 实验步骤、实验内容截图(从创建⼯程开始到仿真结束)

1.路径设置

2.器件选择

3.汇总

4.创建BDF

5.原理图设计

6.编译结果

7.创建VWF进行功能仿真

文章来源:https://www.toymoban.com/news/detail-508230.html

文章来源:https://www.toymoban.com/news/detail-508230.html

波形图中CBA按照000 , 001 , 010 , 011 ....递增文章来源地址https://www.toymoban.com/news/detail-508230.html

到了这里,关于【Quartus | verilog 系列】实现 3-8译码器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!