一、 对比实验

-

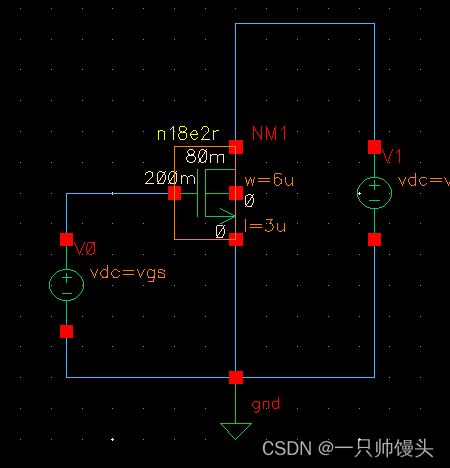

[[CS共源极]]:电流源做负载,衬底接地

文章来源:https://www.toymoban.com/news/detail-508422.html

文章来源:https://www.toymoban.com/news/detail-508422.html -

[[DTMOS]]构成的CS:衬底接栅极

文章来源地址https://www.toymoban.com/news/detail-508422.html

文章来源地址https://www.toymoban.com/news/detail-508422.html

仿真器设置

1. noise 仿真器设置

- 输出端口为单端口时,负极选择gnd

2. main form设置

- 设置需要展示的噪声:

实验结果分析

1. 输入噪声

- DTMOS的CS噪声更大:

2. 增益

- DTMOS的CS增益也更小:

总结

- 在结果显示器中的"Brower"中显示的“noise”,其中的out、in的噪声单位为[[噪声谱PSD]]求根号,直接用“Cacular”来计算其平方,同样可以得到PSD

- noise的增益和电路的增益是等价的

到了这里,关于Cadence仿真笔记(二):传统noise仿真—共源极的噪声的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!