| 设计步骤(分模块叙述,并附上各模块与总体电路图) 1.计时模块,显示模块,调时模块设计

计数器模块由七片74LS160的芯片组成,两片为“秒”,两片为“分”,两片为“时”,还有一片作为“星期”,七个数码管显示器用来显示数字。‘秒’和‘分’采用60进制。通过异步清零的方法将两片74LS160扩展为60进制,在‘秒’十位中,当‘0110’时,接线接QB、QC,两端同时为1,7400N输出0给清零端CLR,60时立刻清零。而“分”和“秒”之间则用一个非门将其连接起来,,即当信号为0110时(即“6”)给一个上升沿脉冲到“分”作为脉冲输入,“分”和“时”之间的级联也是采用的一样的原理。 “时”位采用的是24进制,通过1个与非门控制清零,即到24的时候立刻清零,非门是将信号传导“星期”模块那里。就是当“时”的十位为0010和“时”的个位为0100时产生一个脉冲信号给“星期”模块。 “星期”采用了1~7,用同步置数法,当到达数字7后经过一个周期跳到1,这里用了一个74LS10N芯片来实现。 为了方便时间调整,时间调整功能我用了除系统总脉冲外的另外的脉冲来做调整,通过三个双向开关分别对“星期”“时”“分”进行调整。开关拨到上面就是正常计时,拨到下面就是调时。 2.闹钟模块设计

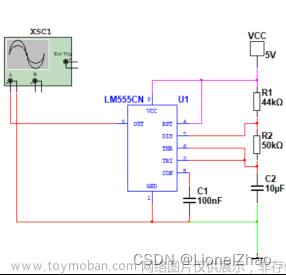

闹钟模块设计思路基本和计数器模块一样。采用了计数器模块里的“分”和“时”的部分,区分是‘分’和‘秒’之间没有非门来连接,都是通过给脉冲信号来进行调时。闹钟模块主要的功能是用来设置时间来和计数器模块做比较。

对比模块由四片4585BD芯片组成,主要功能是用来对比闹钟模块数值和计数器模块数值是否相同。计数模块通过B0~B3输入信号,闹钟模块通过A0~A3输入信号,比较的结果由OAEQB输出。AGTB和ALTB接地,AEQB接5V电压。通过一个与门将四个4585BD芯片的OQEQB连接在一起,四个OQEQB都为1时,与门输出1。这里比较的是“时”和“分”,相同时闹钟响一分钟。这里的闹钟开关是为了防止刚开始仿真时闹钟模块和计数器模块 ‘时’‘分’都为0(即相同)时,与门输出为1时误响。比较结果由一个指示灯与蜂鸣器作为闹铃,当计时模块的时分与闹钟模块的时分完全相同时,OQEQB输出均为1,指示灯亮,蜂鸣器响。

|

| 五、运行结果

当计时模块和闹钟模块时间相同的时候可以看到灯泡亮起,且蜂鸣器发出声音,且持续1分钟。文章来源地址https://www.toymoban.com/news/detail-508509.html |

到了这里,关于电子设计数字钟,multisim仿真·的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

文章来源:https://www.toymoban.com/news/detail-508509.html

文章来源:https://www.toymoban.com/news/detail-508509.html