目录

1、多路选择器简介

2、硬件设计

3、实验任务

4、程序设计

4.1、模块设计

4.2、绘制波形图

4.3、编写代码

(1)assign 中条件运算符(三目运算符)实现方法:

(2)always 语句块中使用 if-else 实现方法:

(3)always 语句块中使用 case 语句的方法:

4.4、仿真验证

4.4.1、编写 TB 文件

4.4.2、仿真验证

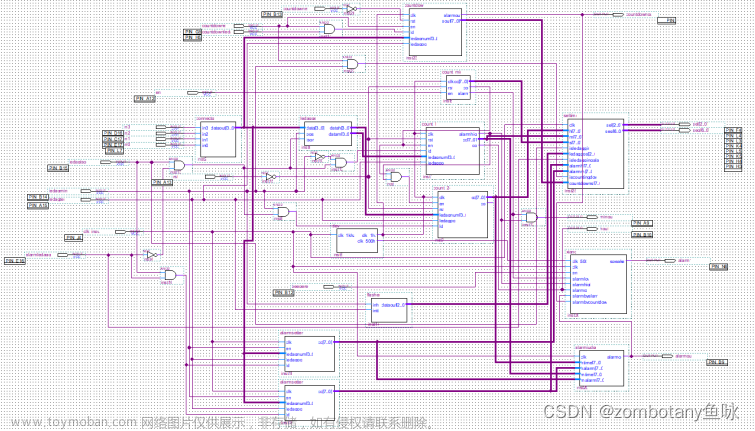

5、RTL 原理图

组合逻辑电路设计---多路选择器

本章开始我们将进行组合逻辑电路的设计学习,多路选择器就是一个数电比较经典入门的逻辑电路。在本章节中,我们将使用 Verilog 语言描述一个具有多路选择器功能的电路,带领大家掌握新的语法知识和基本模块框图、波形、代码设计方法,以及最后通过仿真来验证设计的可行性。

1、多路选择器简介

多路选择器 MUX(multiplexer)是一个多输入、单输出的组合逻辑电路,一个 N 输入的多路选择器就是一个 N 路的数字开关,可以根据通道选择控制信号的不同,从 N 个输入中选取一个输出到公共的输出端。多路选择器也是 FPGA 内部的一个基本资源,主要用于内部信号的选通。简单的多路选择器还可以通过级联生成更大的多路选择器。

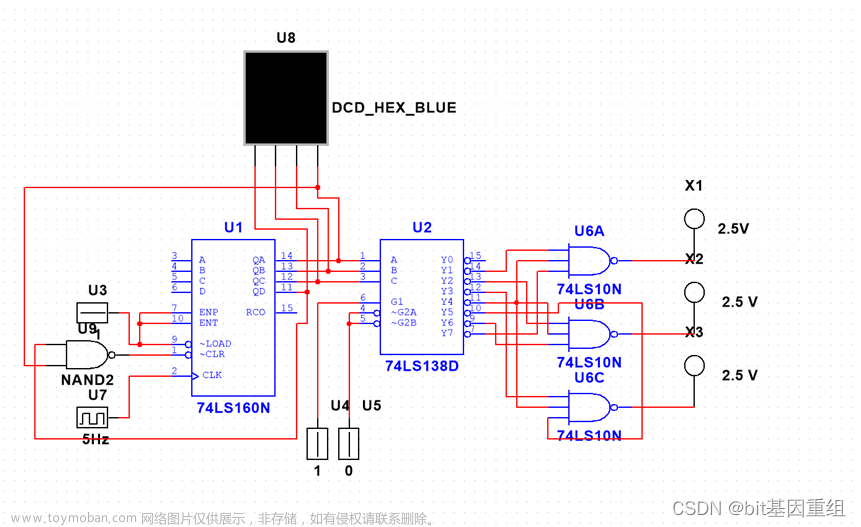

2、硬件设计

开发板上,板载了 5 个按键开关以及 4 个 LED 灯。其中最左边红色按键为 PL 端复位按键,PL 端复位按键右边两个按键连接至 ZYNQ 的 PL 引脚,最右边两个按键连接至 ZYNQ 的 PS 引脚;最左边两个 LED 灯也是连接至 ZTNQ 的 PL 端,最右边两个 LED 灯连接到 PS 端。实物图如下图所示:

底板上按键的原理图如下图所示:

底板上 LED 的原理图如下图所示:

从原理图可以看出,按键默认状态为高电平,按下后为低电平,LED 灯则为高电平点亮。我们只使用 PL 端的外设。图中的每个按键都连接了一个 10K 电阻,起到限流的作用,以防止按键被按下时电源直接接地造成电路短路。

3、实验任务

本节的实验任务是使用 ZYNQ 开发板来设计一个简单的 2 选 1 多路选择器,主要功能是通过选通控制信号 sel 确定输入信号 in1 和 in2 哪一个信号作为输出。当选通控制信号 sel 为 1 时,输出为 A 端信号;当选通控制信号 sel 为 0 时,信号输出为 B 端信号。

4、程序设计

4.1、模块设计

本次实验的功能是一个二选一的多路选择器,因此给模块命名为 mux2_1。模块中的输入为三个 1 位的信号,其中 in1 和 in2 为两个输入信号,sel 为输入的控制信号,out 为单 bit 的输出信号。模块图如下图所示:

根据实验任务所述,可以列出二选一多路选择器的真值表,如下表所示:

由模块图以及真值表可知,本次实验需要三个输入信号,一个输出信号。输入端可以使用 PL 端的两个按键以及一个复位按键,输出端可以使用 PL 端的一个 LED 灯进行表示。

4.2、绘制波形图

由真值表可以看出,当 sel 信号为 1 时,输出信号 out 等于输入信号 in1;当 sel 为 0 时,输出信号 out 等于 in2。

通过上述分析,我们就可以根据真值表进行多路选择器输入与输出波形的绘制。其波形如下图所示:

4.3、编写代码

实现二选一多路选择器功能的 Verilog 代码形式有很多种,这里选择三种不同的语法来实现代码的编写。

(1)assign 中条件运算符(三目运算符)实现方法:

//assign 中条件运算符(三目运算符)实现方法:

module mux2_1(

input in1, //输入信号 in1

input in2, //输入信号 in2

input sel, //选择控制信号 sel

output out //输出信号 out

);

//*****************************************************

//** main code

//*****************************************************

//out:组合逻辑输出选择结果

//此处使用的是条件运算符(三目运算符),当括号里面的条件成立时

//执行"?"后面的结果;如果括号里面的条件不成立时,执行": "后面的结果

assign out = (sel == 1'b1) ? in1 : in2;

endmodule

(2)always 语句块中使用 if-else 实现方法:

//++++++++++++++++++++++++++++++++++++++++++++++++

//(2)always 语句块中使用 if-else 实现方法:

module mux2_1(

input in1, //输入信号 in1

input in2, //输入信号 in2

input sel, //选择控制信号 sel

output reg out //输出信号 out

);

//*****************************************************

//** main code

//*****************************************************

//out:组合逻辑输出选择结果

always@(*) begin //"*"为通配符,在这个模块中的任何一个输入信号或电平发生变化时

if(sel == 1'b1) //该语句下方的模块将被执行。

out <= in1;

else

out <= in2;

end

endmodule

//++++++++++++++++++++++++++++++++++++++++++++++++

(3)always 语句块中使用 case 语句的方法:

//-----------------------------------------------------

//(3)always 语句块中使用 case 语句的方法:

module mux2_1(

input in1, //输入信号 in1

input in2, //输入信号 in2

input sel, //选择控制信号 sel

output reg out //输出信号 out

);

//*****************************************************

//** main code

//*****************************************************

//out:组合逻辑输出选择结果

always@(*) begin

case(sel)

1'b0:

out <= in2;

1'b1:

out <= in1;

//如果 sel 的情况没有全部列举出来一定要加 default

//因为此处 sel 只有两种情况,并且都列举了,所以 defalut 可以省略判断

default: ;

endcase

end

endmodule

//-----------------------------------------------------4.4、仿真验证

4.4.1、编写 TB 文件

TestBench 是用于验证功能模块的设计是否符合预期,主要分为以下三个步骤:

- 1、 向被测功能模块的输入接口添加激励;

- 2、 对被测功能模块的顶层接口进行信号例化;

- 3、 判断被测功能模块的输出是否满足设计预期。

二选一多路选择器模块的输入端口为 in1、in2 和 sel,输出 out 是根据控制选择信号的变化,而选择输出 in1 或者 in2 的。所以我们仿真只需要对 in1、in2 和 sel 进行激励就可以得到输出信号 out 的仿真。

二选一多路选择器 TB 模块(tb_flow_led.v)代码编写如下:

//仿真验证

//编写 TB 文件

//TestBench 是用于验证功能模块的设计是否符合预期,主要分为以下三个步骤:

//1、 向被测功能模块的输入接口添加激励;

//2、 对被测功能模块的顶层接口进行信号例化;

//3、 判断被测功能模块的输出是否满足设计预期。

//二选一多路选择器模块的输入端口为 in1、in2 和 sel,

//输出 out 是根据控制选择信号的变化,而选择输出 in1 或者 in2 的。

//所以我们仿真只需要对 in1、in2 和 sel 进行激励就可以得到输出信号 out 的仿真。

//二选一多路选择器 TB 模块(tb_flow_led.v)代码编写如下:

`timescale 1ns / 1ns

module tb_mux2_1();

reg in1;

reg in2;

reg sel;

wire out;

//initial 语句是不可以被综合的,一般只在 testbench 中表达而不在 RTL 代码中表达。

initial begin //在仿真中 begin...end 块中的内容都是顺序执行的

in1 = 1'b0; //初始状态赋值

in2 = 1'b0;

sel = 1'b0;

#100 //经过 100ns 的延时

in1 = 1'b0; //100ns 时的输入值

in2 = 1'b0;

sel = 1'b1;

#100 //经过 200ns 的延时

in1 = 1'b0; //200ns 时的输入值

in2 = 1'b1;

sel = 1'b0;

#100 //经过 300ns 的延时

in1 = 1'b0; //300ns 时的输入值

in2 = 1'b1;

sel = 1'b1;

#100 //经过 400ns 的延时

in1 = 1'b1; //400ns 时的输入值

in2 = 1'b0;

sel = 1'b0;

#100 //经过 500ns 的延时

in1 = 1'b1; //500ns 时的输入值

in2 = 1'b0;

sel = 1'b1;

#100 //经过 600ns 的延时

in1 = 1'b1; //600ns 时的输入值

in2 = 1'b1;

sel = 1'b1;

end

mux2_1 u_mux2_1(

.in1 (in1 ), //输入信号 in1

.in2 (in2 ), //输入信号 in2

.sel (sel ), //选择控制信号 sel

.out (out ) //输出信号 out

);

endmodule

程序中第一行代码定义的 1ns / 1ns 表示仿真单位和仿真精度都是 1ns。

在 testbench 中端口列表为空,所以第三行模块为空,而在 initial 和 always 语句块中的变量一定是为 reg 型变量,输入的变量是需要我们手动激励的,所以一定要为 reg 型变量。而输出变量在 testbench 中一般都是为 wire 型变量。

在第十一行到第四十行使用了 initial 语句块,第十三行到第十五行首先进行对各输入信号的初始化,在初始化完成后需要对各输入端口数据进行模拟。然后每 100ns 对各输入端口进行赋值,产生的数据完成对输入端口的激励。

在完成信号的激励后,我们就可以进行测试模块的实例化,其中 mux2_1 为被实例化模块的名字, u_mux2_1 为我们实例化之后定义的名字。

4.4.2、仿真验证

接下来打开 Modelsim 软件对代码进行仿真,在运行仿真 1us 后,仿真的波形如下图所示:

由上图可知,图 10.4.3 mux2_1 仿真波形 a 中 sel=1’b0,in2=1’b1,out=1’b1;在图 10.4.4 mux2_1 仿真波形 b 中 sel=1’b1,in1=1’b0,out=1’b0。仿真结果与我们列出的真值表结果是相对应的,大家如果有兴趣可以多选取几组波形与真值表进行对比。

5、RTL 原理图

在完成了代码设计之后,可以通过 Vivado 软件查看 RTL 分析原理图,通过原理图可以快速掌握项目设计的架构图,方便后续对代码进行优化。在左侧导航栏点击 Schematic(位于 Flow Navigator→RTL ANALYSIS →Open Elaborated Design→Schematic),打开 RTL 原理图设计,如下图所示:

。。

。。 文章来源:https://www.toymoban.com/news/detail-508824.html

文章来源:https://www.toymoban.com/news/detail-508824.html

由上图可以清晰地看到代码和电路图的对应关系,RTL_MUX 是选择器,in1 和 in2 两个输入信号,根据控制选择信号 sel 的数据来进行输出选择。值得一提的是,Vivado 软件中的 RTL 分析原理图只针对 RTL 层面,并不是代码和 FPGA 器件内部资源的对应关系图,如果想要查看代码和 FPGA 内部资源的对应关系可以查看综合后的原理图,可以先对代码进行综合,然后找到 Flow Navigator→SYNTHESIS→Open Synthesized Design→Schematic,大家可以自行打开查看。文章来源地址https://www.toymoban.com/news/detail-508824.html

到了这里,关于组合逻辑电路设计---多路选择器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA 学习记录] 简单组合逻辑——多路选择器](https://imgs.yssmx.com/Uploads/2024/02/777306-1.gif)