「FPGA」基本时序电路元件——锁存器和触发器

FPGA是一种数字电路实现的方式,它是基于小型查找表(16X1)设计的,它的兄弟CPLD是基于高密度复杂组合逻辑设计的。FPGA的一个优点是触发器资源丰富,适合实现复杂的时序设计。本文将从 门级电路的角度来介绍时序电路的基本结构,锁存器(Latch)和触发器(flip-flop)。实际上,还可以直接使用晶体管来构建锁存器和触发器,这样更节约。

1. 最简单的双稳态元件

双稳态元件是记忆电路的基础,它的特点是有两个稳定状态(Q=1,Q=0),当外界无外来触发信号的时候,它将保持上一个状态。

最简单的双稳态元件是交叉耦合的反相器,如图1。当Q=1的时候,下面反相器的输入为1,输出为0,即Q-=0,这个输出0又作为上面反相器的输入,从而进一步“巩固”Q=1。Q=0同理。

不过,这个电路是没有使用价值的,因为没有输入,其状态完全由一个无法控制的初始状态决定,Q=1则一直为1,Q=0则一直为0。因此,具有实用价值的是它的改进版,锁存器和触发器。

2. SR锁存器

其中S是set的首字母,表示置位,R是reset的首字母,表示复位。它的组成是两个交叉耦合的或非门,如图2,其中绿线表示高电平,灰线表示地电平。当S=1,R=0的时候,Q=1,Q-=0。当R=0时,与的结果一定是0,则其上面的或非门的输出Q=1。Q=1作为下面的或非门的输入,同时S=1,两个1相或结果为1,则下面的或非门的输出为0。

当S=0,R=1的时候,Q=0,Q-=1。分析同理。

当S=0,R=0的时候,这两个或非门和两个反相器在逻辑功能上没有区别。当一个或非门的一端输入常为0,那么当另外一端输入为1,输出为0,另一端输入为0,则输出为1。其分析可参考交叉耦合反相器。该锁存器将保持原有的状态。

当S=1,R=1的时候,由于或门是有1为1,因此两个或非门的输出都是0。这是一个混乱的电路响应(正常的Q和Q-应互为相反数)。

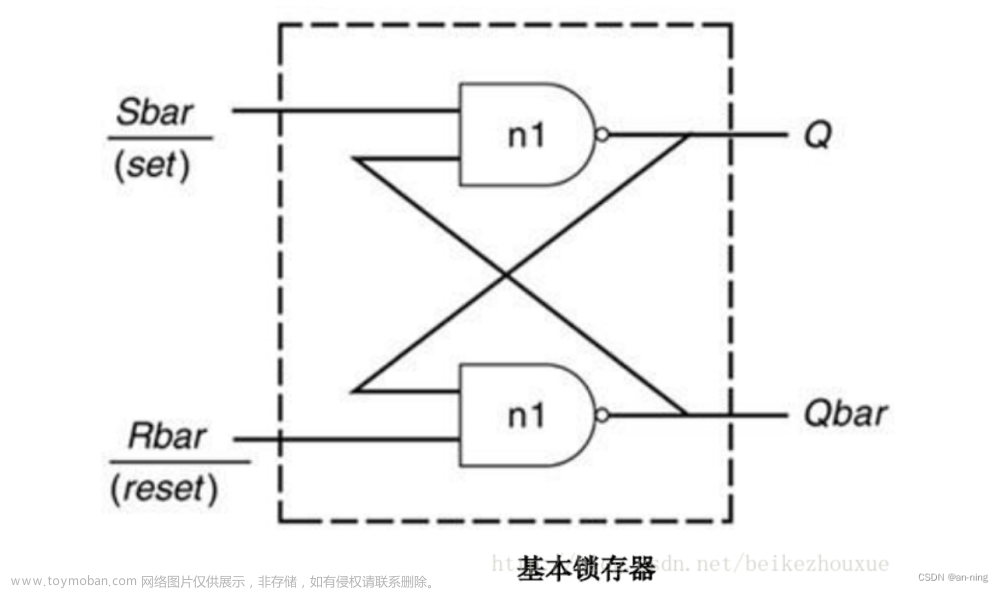

值得注意的是,以上电路是采用或非门实现的SR锁存器,实际上,我们可以,只要满足上述输入输出关系的元件都是SR锁存器。比如可以采用与非门实现SR锁存器,如图3。注意区别,当S=0,R=0时,该器件无效,当S=1,R=1时,该器件保持。

3. D锁存器(data latch)

SR锁存器可以在Q上储存一个1bit的状态值,还可以通过S和R来控制Q=1或者是Q=0。但是这种设计有个缺陷,我们不知道什么时候进行置位和复位。或句话说,SR锁存器在时间和内容上是混在一起的。

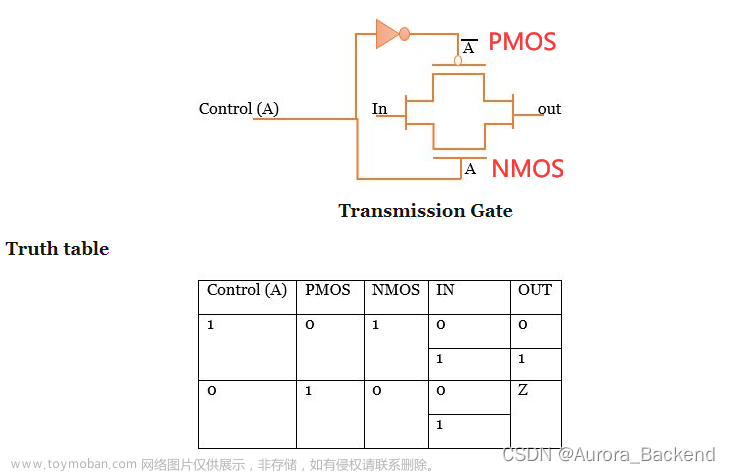

因此,对电路进行改进,引入一路时钟信号(占空比为50%的方波),当时钟信号为高电平的时候,才让数据信号(D)作用在SR锁存器的S端,并直接体现在Q上,就好像一根导线,用专业术语叫透明(transparent)。当时钟信号为低电平的时候,SR锁存器保持,就好像把数据信号阻断了一样,叫不透明(opaque)。要实现该功能,需要在外侧加入两个与门,其电路结构如图4。

D锁存器又称电平敏感锁存器。

4. D触发器

触发器的英文是flip-flop,flip是轻抛,flop是重重地落下。相比于电平敏感的D锁存器,D触发器是上跳沿敏感的,只有当时钟CLK从低电平变化到高电平的时候,电路才是透明的。所以其实现可以是,用两个D锁存器,第一个锁存器在时钟低电平的时候储存D的值,当变化成高电平的时候,再将储存的值送到第二个D锁存器中。

如图5,左图是当CLK为低电平时,下侧的D锁存器(又称“主锁存器”),读入输入数据,右图是当CLK为高电平时,上侧的D锁存器(又称“从锁存器”),将主锁存器的输出作为输入。

5. 寄存器(register)

寄存器的概念,最开始接触,可能是在学习C语言的时候。那个时候刚刚接触到内存,知道一个变量的值是被储存在某个地址对应的内存空间,内存则是由寄存器构成的。然后如果使用到一些微处理器,也会接触到寄存器的概念,通过对某些寄存器写入特定值,从而设置微处理器的工作模式。

所谓寄存器,是由共用一路时钟的一列D触发器构成。图6所示的寄存器,被设置成1001。文章来源:https://www.toymoban.com/news/detail-509162.html

文章来源地址https://www.toymoban.com/news/detail-509162.html

文章来源地址https://www.toymoban.com/news/detail-509162.html

小结

- 交叉耦合反相器是记忆元件,但不能控制输入,不具有实用性。

- SR锁存器可以设置输出为0或者1,但是没有时间的概念。需要两个或非门或者两个与非门。

- D锁存器是在SR锁存器的基础上,增加了两个与门和一路时钟信号,CLK为低电平,两个与门都不通,SR Latch保持,CLK为高电平,根据D是高还是低,分别让SR锁存器出现置位和复位。

- D触发器是两个D Latch背靠背相连接而成,两个锁存器的CLK信号相反。低电平时,先将D存入第一个锁存器,高电平时,再将第一个锁存器的输出送入第二个锁存器。因此只在低电平接收数据,上跳时改变数据,高电平送出数据。

- 寄存器就是一摞触发器。

- 此外还有带使能端的触发器、带复位端的触发器。

到了这里,关于「FPGA」基本时序电路元件——锁存器和触发器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!