1. 半加器

1.1 定义

半加器,就是不考虑进位的加法器,只有两个输入和两个输出:输入A和B,输出和数sum和进位cout,半加器真值表如下:

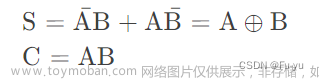

1.2 关系表达式

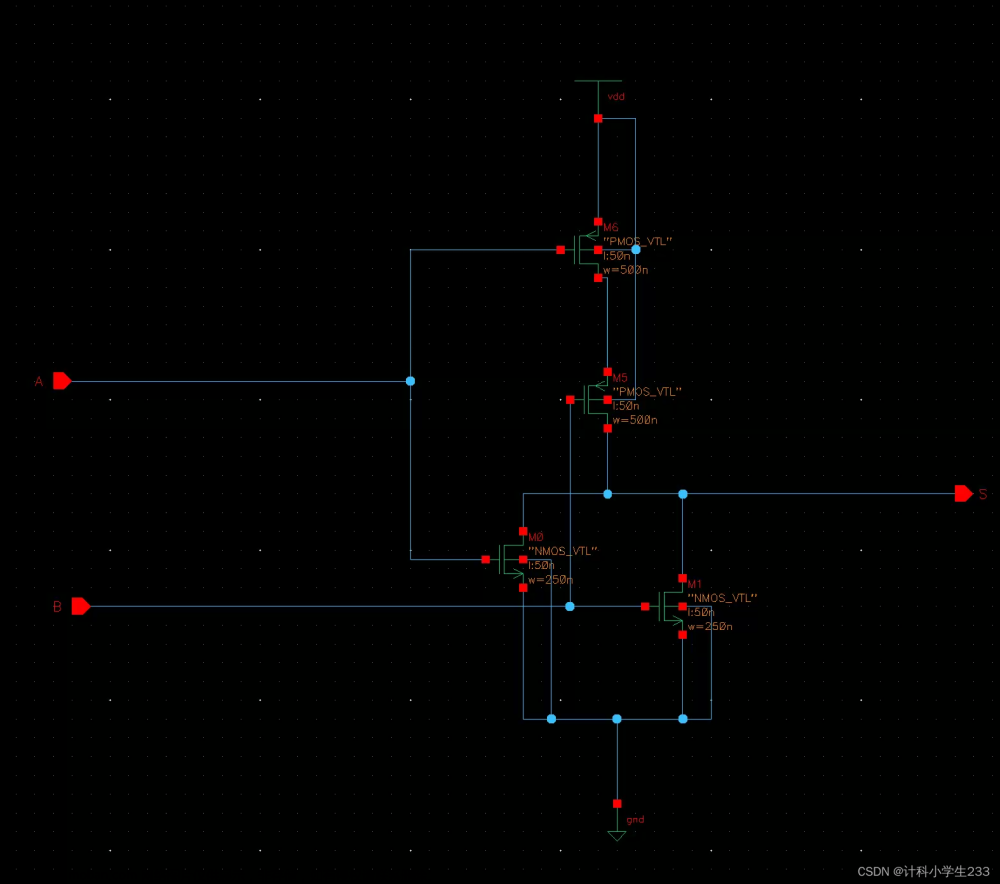

1.3 电路设计

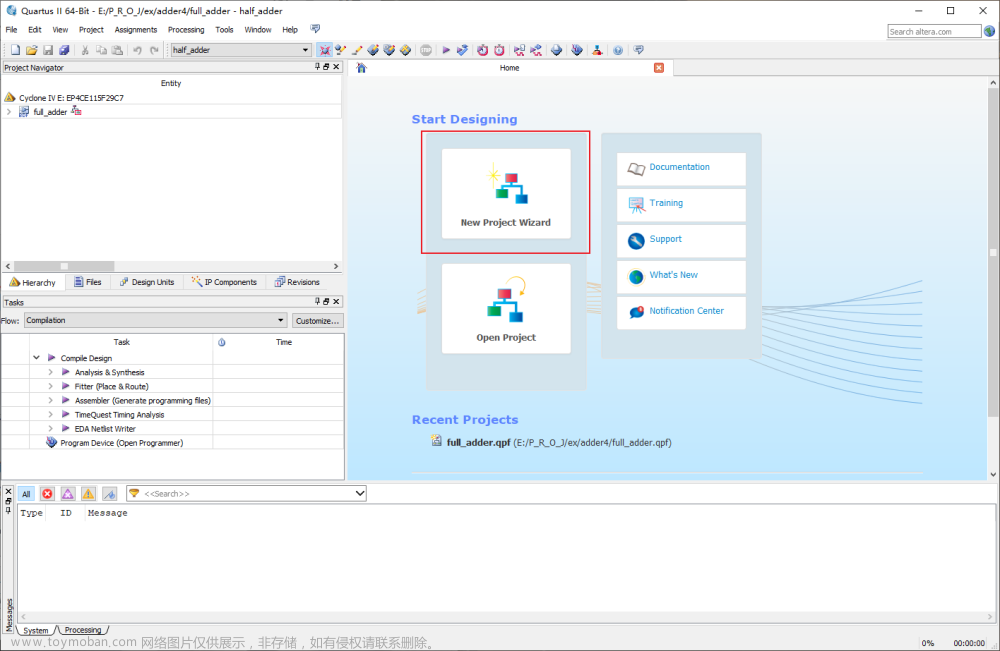

1.4 代码实现

module add_half(

input A ,

input B ,

output wire S ,

output wire C

);

assign S = A ^ B;

assign C = A & B;

endmodule

2. 全加器

2.1 定义

全加器就是在半加器的基础上引入一个进位输入,总共三个输入两个输出。全加器真值表如下:

2.2 关系表达式

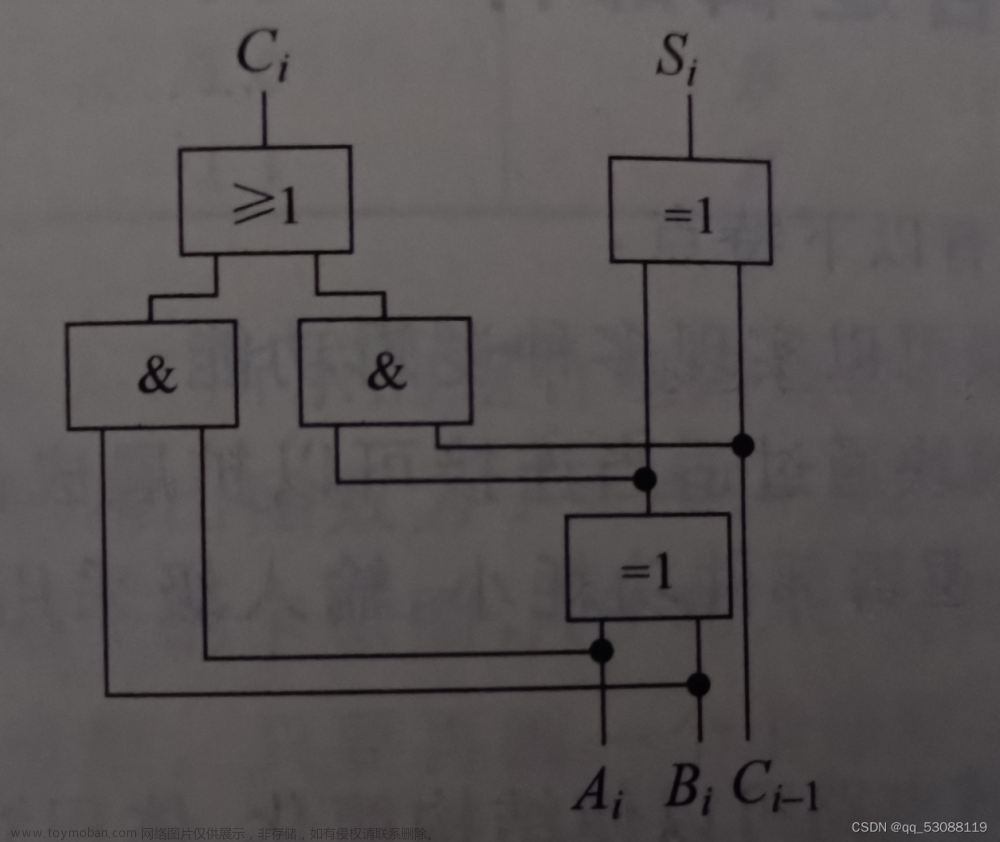

这里的输出一共有两个,一个sum,一个进位cout。sum的值是A+B+cin然后去掉进位得到的,也就是说A、B、cin 中,如果输入1的个数是奇数,则sum为1,输入1的个数为偶数(含零)则sum为0。根据这个奇偶判定,可以想到用异或操作,所以得到表达式:

cout的值也好分析,cout是加和出来的进位,也就是说,如果A、B、cin三个数中,有两个及以上个1,则cout为1,这个容易得到表达式:

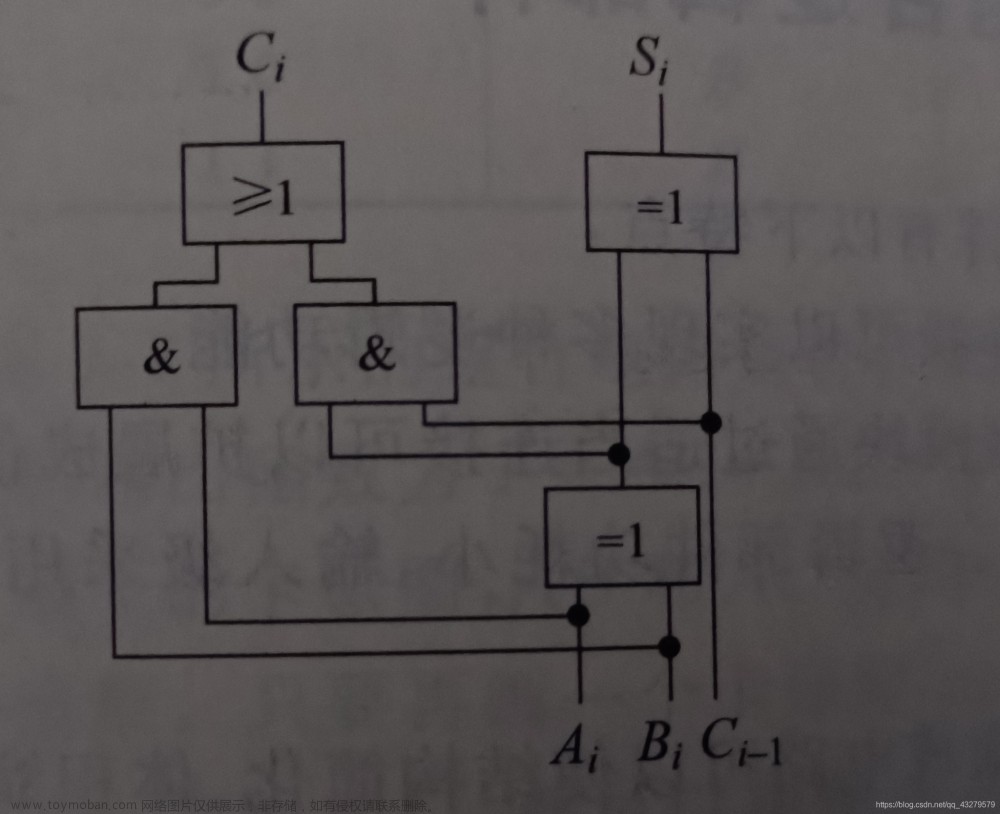

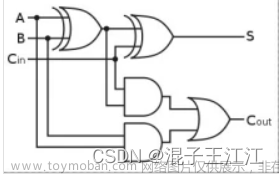

2.3 电路设计

2.4 代码实现

module add_full(

input A ,

input B ,

input Ci ,

output wire S ,

output wire Co

);

assign S = A ^ B ^ Ci;

assign Co = A&B | A&Ci | B&Ci;

endmodule

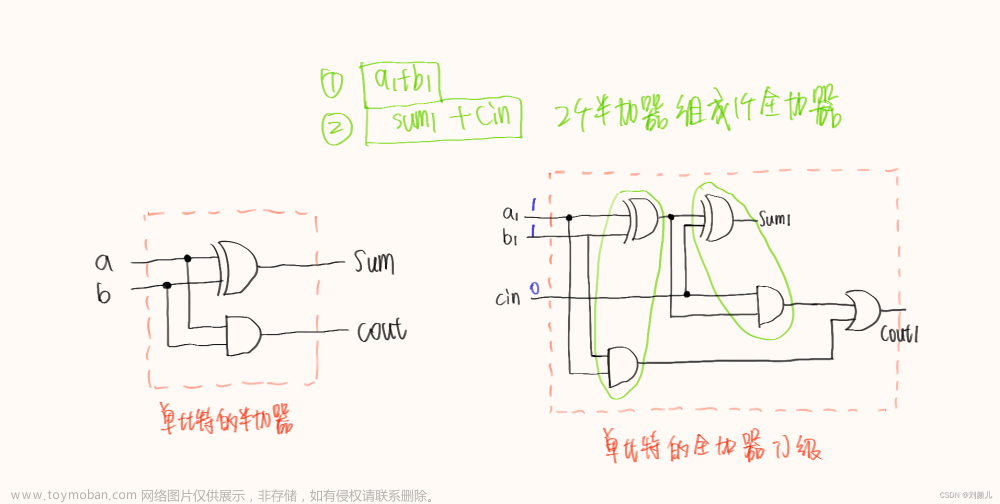

3. 两个半加器 实现 一个全加器

3.1 设计电路图

3.2 代码实现

`timescale 1ns/1ns

module add_half(

input A ,

input B ,

output wire S ,

output wire C

);

assign S = A ^ B;

assign C = A & B;

endmodule

/***************************************************************/

module add_full(

input A ,

input B ,

input Ci ,

output wire S ,

output wire Co

);

wire [1:0] s, c;

add_half m1 (

.A(A),

.B(B),

.S(s[0]),

.C(c[0]));

add_half m2 (

.A(s[0]),

.B(Ci),

.S(s[1]),

.C(c[1]));

assign S = s[1];

assign Co = c[0] | c[1];

endmodule

其实这是一道公司笔试题目,大家可以点击这里

参考文献

文献1

文献2

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!文章来源:https://www.toymoban.com/news/detail-509341.html

如果觉得对你有用的话,记得收藏+评论!!!文章来源地址https://www.toymoban.com/news/detail-509341.html

到了这里,关于【基础知识】~ 半加器 & 全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!