E1.E2.E3为三个使能输入端,其中E1和E2为低有效,E3为高有效,除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高;

当S1 = 0 或S2’ + S3’ = 1 时,译码器被禁止工作,当S1 = 1时,S2’+S3’ = 0 时,译码器处于工作状态。

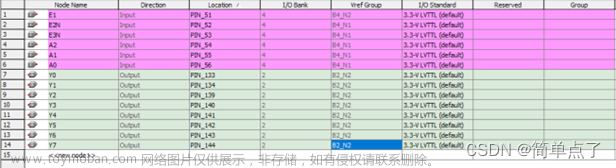

A0,A1,A2为3位二进制加权地址输入端口,A2A1A0顺序组成的3位2进制数对应的十进制数x控制使能端口Yx’;例如当A2A1A0 = 101 时,其他门输出端全为高电平,只有Y5’为低电平。

Y0-Y7为8个输出端口,其输出电平由A0,A2,A3,E1,E2,E3决定。

逻辑功能表

文章来源:https://www.toymoban.com/news/detail-509423.html

文章来源:https://www.toymoban.com/news/detail-509423.html

在单片机上的应用

74HC138芯片在单片机上最常见的用处就是IO扩展,通常配合74HC573锁存器使用,例如在蓝桥杯单片机开发板上面,74HC138译码器和74HC573锁存器的联合使用就可以实现3+8个IO口控制32个IO口的输出等。文章来源地址https://www.toymoban.com/news/detail-509423.html

到了这里,关于138译码器的工作原理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!