1 简介

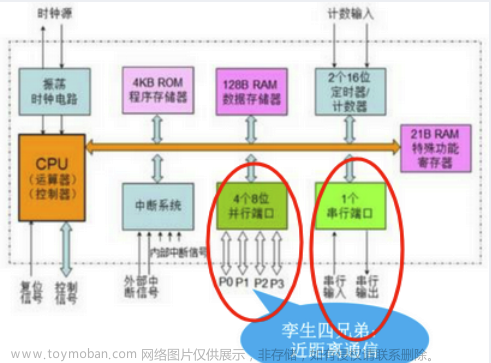

AT89C51/C52是指两个系列的产品,具体包含AT89C51、AT89C52,但是最小系统的组成基本上相差不大。最小系统通常包括:电源、复位、时钟、程序下载。

2 最小系统分析

讲解内容以AT89C52为例,对AT89C52最小系统进行详细讲解。

2.1 电源设计

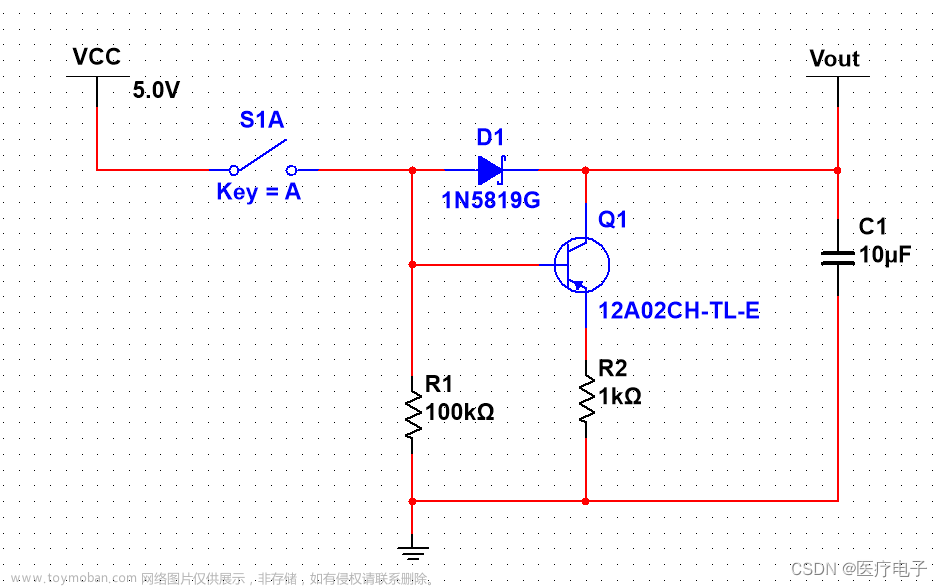

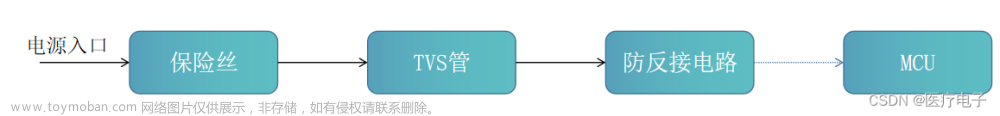

与STM32不同,AT89C52不仅可以3.3V供电,还能使用5V进行供电。通常情况下,单片机的供电时5V。其中EA为高时,选择内部程序存储。

2.2 复位电路设计

与STM32不同,AT89C52采用的高电平复位。系统正常工作时,复位管脚为低电平,系统复位时,将复位管脚拉高,整个系统将回到复位状态。文章来源:https://www.toymoban.com/news/detail-509493.html

2.3 时钟电路

AT89C52的晶振电路采用的22.1184MHz的晶振,通常采用12MHz的晶振比较多。匹配电容的计算方式,请参考这篇文章:晶振匹配电容和电阻的计算。文章来源地址https://www.toymoban.com/news/detail-509493.html

到了这里,关于数字电路硬件设计系列(五)之AT89C51/C52最小系统设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!