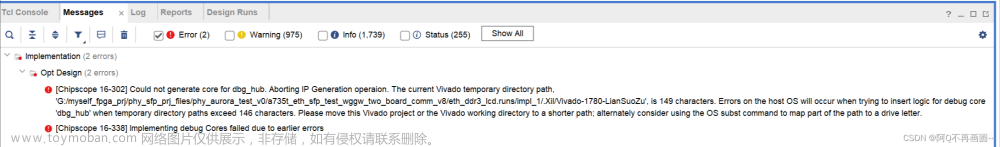

我们在使用vivado的时候,做完了一些模块以后,进行仿真的时候会出现以下错误:

[USF-XSim-62] 'compile' step failed with error(s). Please check the Tcl console output or 'C:/Users/gongdell/ddc/ddc.sim/sim_1/behav/xsim/xvlog.log' file for more information.

在正常情况下,vivado会指出你的代码错误的那一行,你可以直接点击,然后直接对错误的哪一行进行修改。但是有的时候是没有指出那一行错误,这就需要下面的解决办法了。

楼主也是郁闷了很久,因为写完程序的时候,没有报错,但是仿真就是转不动。于是按照错误提示当中的路径去打开了对应的文档一看,如下图所示:

可以看到我们这里的文档已经指出了错误,凡是ERROR的选项,都是需要纠正的。错误有什么呢?原来是重复定义了,上面定义过了,后面再定义一次,在写完.v文件时不会报错,但是仿真时就会报错,需要修改。这是代码不规范引起的错误。

不规范的行为有:

1.先使用了,但是在后边才定义。(虽说verilog是并行语言,但这么写会有警告)

2.重复定义一个wire或者reg,在一个文件里,反复定义,仿真会报错,文件里面是警告。

3.未定义,直接使用,会报警告。

4.定义错误,把一个变量即定义为reg,又定义为wire。

等等,不再赘述。

楼主给uu们的建议是打开你提示的路径里面的文档,看看里面有那些ERROR,在对症下药。文章来源:https://www.toymoban.com/news/detail-510165.html

亲测可用,蟹蟹朋友们。文章来源地址https://www.toymoban.com/news/detail-510165.html

到了这里,关于vivado报错:USF-XSim-62的常见解决办法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![【Vivado】 [Place 30-574] 时钟使用普通IO时的报错解决办法](https://imgs.yssmx.com/Uploads/2024/02/506736-1.png)