1、前言

目前USB3.0的实现方案很多,但就简单好用的角度而言,FT601应该是最佳方案,因为它电路设计简单,操作时序简单,软件驱动简单,官方甚至提供了包括FPGA驱动在内的丰富的驱动源码和测试软件;

本设计用FPGA驱动FT601芯片实现USB3.0数据通信,使用同步245模式通信,提供2套vivado工程源码,一套是verilog代码生成的彩条视频经过图像三帧缓存至DDR3后读出,图像给到FT601发送出去,PC机读取FT601发来的视频,并用QT上位机接收视频并显示出来,该工程针对的是手里没有摄像头或者视频输入源的朋友;如果你手里有OV5640摄像头,那么适合第2套工程,第2套工程是采集OV5640摄像头数据,视频经过图像三帧缓存至DDR3后读出,图像给到FT601发送出去,PC机读取FT601发来的视频,并用QT上位机接收视频并显示出来;

本设计完全可以模拟和实现USB3.0相机的功能;代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的USB3.0通信和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式以及上板调试的演示视频放在了文章末尾,请耐心看到最后;

2、FT601芯片解读和时序分析

FT601功能和硬件电路

FT600/601Q 的技术参数如下:

FT600&601Q 芯片是 FT 最新推出的 USB3.0 to FIFO interface IC,实现 USB3.0 与 16/32bit 并行 IO 接口之间的数据传输。

整个 USB 通信协议全部由芯片驱动自行完成,开发者无须考虑 USB 底层固件的编程。

兼容支持 USB3.0(5Gbps),向下兼容 USB2.0(480Mbps and 12Mbps)传输。

高达 8 个可配置 Endpoint. >>支持 2 种 FIFO 传输协议,最大传输可达 400MB/s。

芯片内部有 16K 字节的缓冲区,可以进行数据的大吞吐量操作。

支持远程唤醒功能。

芯片支持多种 IO 电压:1.8V,2.5V.3.3V。

通过 16bit D[O:15]或 32bit D[0:31]并行数据线和读写状态/控制线 RXF、TXE、RD、WR,加上时钟 CLK,使

能 OE 信号线就可实现与 CPU/FPGA 的数据交换。

该芯片内部集成 1.0V LDO,可提供给芯片核心部分使用。

工业级芯片,工作温度范围-40 to 85℃。

芯片框架如下:

外围电路设计参考如下:

FT600/601Q 支持的多种传输模式,其中 245 Synchronous FIFO 模式和 Multi-Channel FIFO 模式是我们最常用的模式。我们这里介绍的 demo 以 245 Synchronous FIFO 模式为例;传输模式通过GPIO引脚高低电平配置,配置真值表如下:

FT601读时序解读

245 Synchronous FIFO 模式读时序如下:

RXF_N为读数据状态信号,RXF_N为低电平期间FPGA可以读取FT601数据;

检测到RXF_N低电平后,拉低OE_N和RD_N,然后开始读数据;

检测到RXF_N高电平后,拉高OE_N和RD_N,然后退出读数据状态;

FT601写时序解读

245 Synchronous FIFO 模式写时序如下:

TXF_N为读数据状态信号,RXF_N为低电平期间FPGA向FT601写入数据;

检测到TXF_N低电平后,拉低WR_N,然后开始向FT601写入数据;

检测到TXF_N高电平后,拉高WR_N,然后退出写数据状态;

3、我这儿的 FT601 USB3.0通信方案

我这儿现有的FPGA基于FT601和FT602的USB3.0通信方案主要有简单的测速方案、图像传输方案,图像传输方案包括简单的彩条传输采集、OV5640摄像头传输采集、HDMI视频采集,HDMI视频采集抓拍、USB3.0 UVC视频等等,所有工方案均包括FPGA工程和QT上位机源码;感兴趣的可以去我的FT601 USB3.0通信专栏阅读,专栏地址如下:

https://blog.csdn.net/qq_41667729/category_12339160.html?spm=1001.2014.3001.5482

4、vivado工程1–彩条视频采集传输

开发板FPGA型号:xc7k325tffg900-2;

开发环境:vivado2022.2;

输入:彩条视频;

输出:FT601–USB3.0接口;

应用:模拟和实现USB3.0相机的功能;

详细设计框图及其原理

详细设计框图如下:

彩条视频:

用verilog代码生成一个VGA时序的,分辨率为1280x720@60Hz的彩条视频,完全可以模拟各种相机和视频输入设备,手里没有摄像头或者板子没有视频输入接口的兄弟可以拿这个东西去用,很实用;

FDMA图像缓存:

FDMA图像三帧缓存,经常看我文章的兄弟都知道,这是我惯用的图像缓存套路,它由FDMA控制器和FDMA构成,作用是将输入的视频缓存到DDR3里做三帧缓存后再读出来,目的是使得图像数据的输入输出跨时钟域读写,输出图像平稳无撕裂等现象;关于FDMA的详细设计说明,请参考我之前的文章:点击直接前往

FT601 模块:

就是FT601的verilog驱动代码,根据FT601芯片读写时序实现接口对接,这里很简单;关于FT601驱动的详细设计说明,请参考我之前的文章:点击直接前往

FT601 驱动:

这是官方给的FT601 驱动,文件已包含在了我提供的资料包里;

QT上位机:

基于c++的QT,调用官方API,实现USB3.0接口的视频数据实时采集并显示,我提供的资料包里有QT上位机软件和QT源码,做嵌入式软件开发的兄弟可以拿去参考;

vivado工程解读

工程Block Design如下:

综合后的工程代码架构如下:

综合编译完成后的FPGA资源消耗和功耗预估如下:

5、vivado工程2–OV5640视频采集传输

开发板FPGA型号:xc7k325tffg900-2;

开发环境:vivado2022.2;

输入:OV5640摄像头;

输出:FT601–USB3.0接口;

应用:模拟和实现USB3.0相机的功能;

详细设计框图及其原理

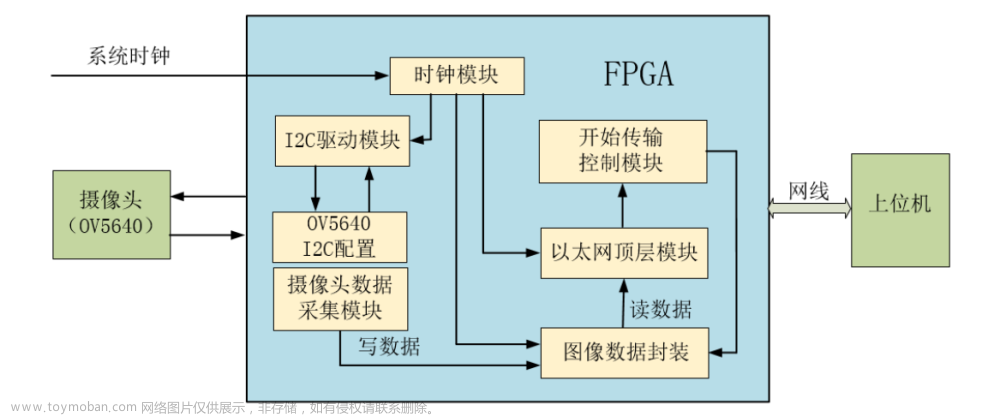

详细设计框图如下:

OV5640摄像头和视频采集:

OV5640分辨率为1280x720@60Hz,纯verilog实现的i2c协议实现对齐内部寄存器的配置,纯verilog实现的图像采集模块将OV5640输出视频采集为VGA时序的RGB888视频输出;

FDMA图像缓存:

FDMA图像三帧缓存,经常看我文章的兄弟都知道,这是我惯用的图像缓存套路,它由FDMA控制器和FDMA构成,作用是将输入的视频缓存到DDR3里做三帧缓存后再读出来,目的是使得图像数据的输入输出跨时钟域读写,输出图像平稳无撕裂等现象;关于FDMA的详细设计说明,请参考我之前的文章:点击直接前往

FT601 模块:

就是FT601的verilog驱动代码,根据FT601芯片读写时序实现接口对接,这里很简单;关于FT601驱动的详细设计说明,请参考我之前的文章:点击直接前往

FT601 驱动:

这是官方给的FT601 驱动,文件已包含在了我提供的资料包里;

QT上位机:

基于c++的QT,调用官方API,实现USB3.0接口的视频数据实时采集并显示,我提供的资料包里有QT上位机软件和QT源码,做嵌入式软件开发的兄弟可以拿去参考;

vivado工程解读

工程Block Design如下:

综合后的工程代码架构如下:

综合编译完成后的FPGA资源消耗和功耗预估如下:

6、上板调试验证

先连接板子和电脑,然后打开QT上位机软件,资料包里的目录如下:

彩条工程输出QT接收结果:

ila波形抓取如下:

OV5640工程输出QT接收结果: 文章来源:https://www.toymoban.com/news/detail-511399.html

文章来源:https://www.toymoban.com/news/detail-511399.html

7、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式1:私,或者文章末尾的V名片。

网盘资料如下: 文章来源地址https://www.toymoban.com/news/detail-511399.html

文章来源地址https://www.toymoban.com/news/detail-511399.html

到了这里,关于FPGA驱动FT601实现USB3.0相机 OV5640视频采集 提供2套工程源码和QT上位机源码的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!