前言

-

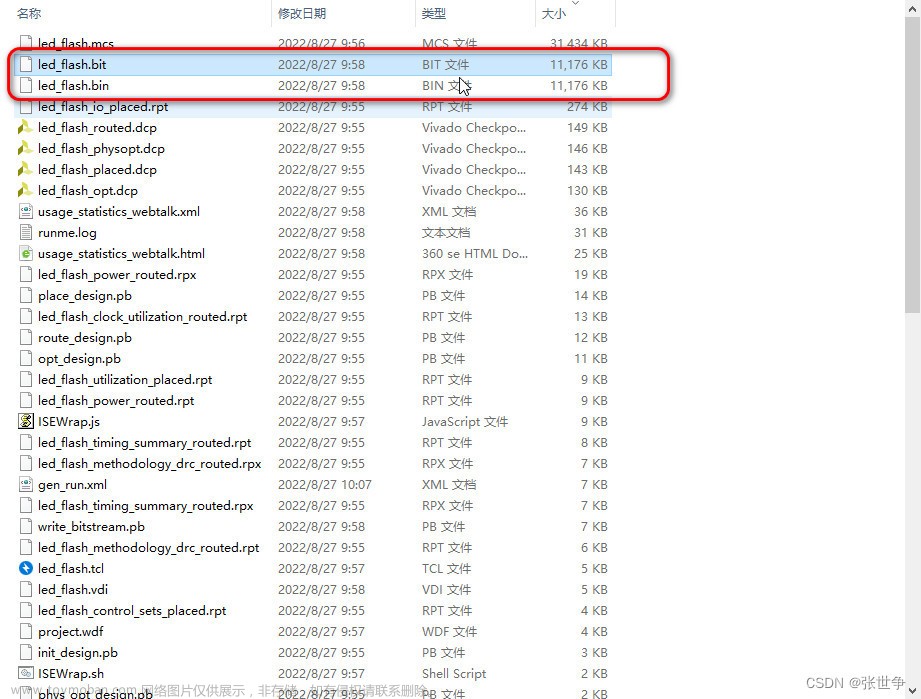

FPGA 不同系列,型号有些区别,并且不同型号FPGA 工程生成的 bit 文件,无法下载

-

当前最好的方式是每个型号都重新创建一个工程,不过这样多少有点繁琐,Vivado可以更改FPGA型号

更改方法

-

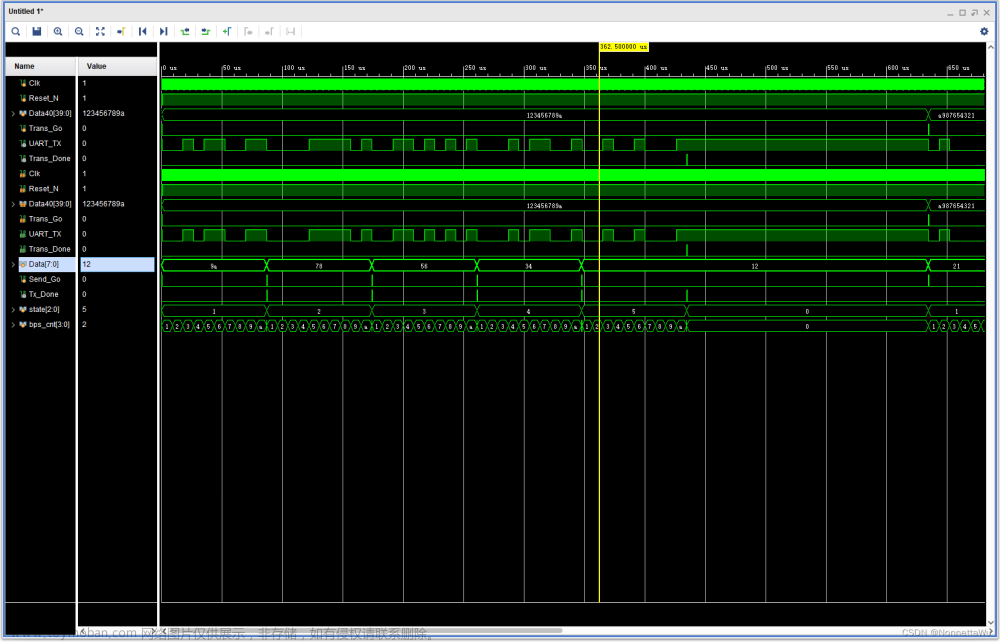

设置里面,可以查看当前的FPGA型号

-

也可以通过【Window】 -> 【Project Summary】,查看当前工程的FPGA 型号

- 点击当前项目的【FPGA 型号】

- 选择新的FPGA型号

文章来源:https://www.toymoban.com/news/detail-512930.html

文章来源:https://www.toymoban.com/news/detail-512930.html

- 跟新建工程时选择 FPGA 一致

文章来源地址https://www.toymoban.com/news/detail-512930.html

文章来源地址https://www.toymoban.com/news/detail-512930.html

- 型号更改成新的了

到了这里,关于FPGA 学习笔记:Vivado 工程更改FPGA 型号的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!