目录

学习目标:

学习内容:

1.PLI的使用

2.PLI任务的连接和调用

3.内部数据的获取

4.PLI库子程序

学习时间:

学习产出:

学习目标:

解释在Verilog仿真中如何使用PLI子程序。

描述PLI的用途。

定义用户自定义系统任务和函数以及用户自定义C子程序。

理解用户自定义系统任务的连接和调用。

从概念上解释在 Verilog 仿真器内部如何表示PLI

区别并描述怎样使用两类PLI库子程序:access子程序和 utility子程序。

学习如何创建用户自定义系统任务和函数,并学习如何在仿真中使用它们。

学习内容:

1.PLI的使用

由于PLI允许用户自己定义实用工具来存取(读、写或修改)表示设计的内部数据结构,因此它具有强大的能力,可以对Verilog语言的功能进行扩展。PLI具有很多种用途,如下所示:

PLI可用于定义其他系统任务和函数。典型的例子有监控任务、激励任务、调试任务和复杂操作等,这些任务和操作难以用标准的 Verilog 结构实现。

一些应用软件.比如翻译器和延迟计算工具,可以用PLI编写。

PLI可用于提取设计信息,比如层次.互连、扇出以及特定类型逻辑元件的数目等。 PLI可用于编写专用或自定义的输出显示子程序。波形观察器可用它生成波形、逻辑互连、源代码浏览器和层次信息。

为仿真提供激励的子程序也可以用PLI编写。激励可以自动生成或者从其他形式的激励转换而来。

普通的基于Verilog 的应用软件可以用PLI子程序编写。这种软件可以与任何Verilog 仿真器—起工作,因为PLI接口提供了统一的存取方式。

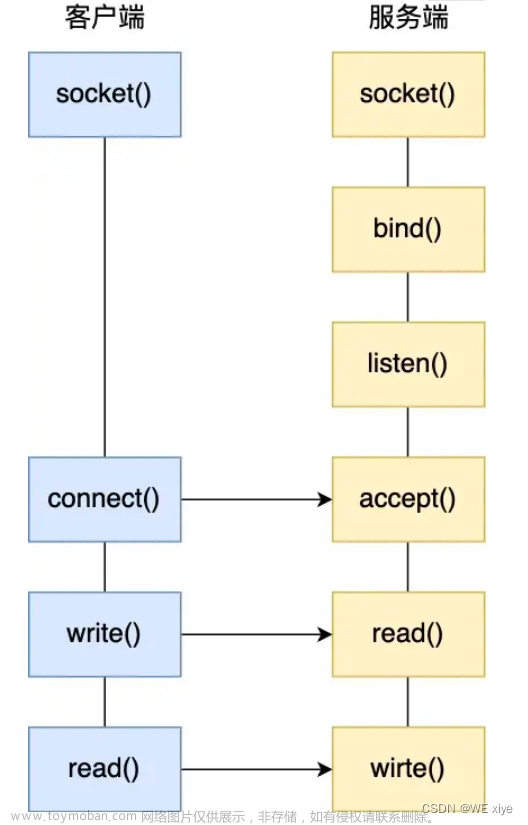

2.PLI任务的连接和调用

设计者可以通过使用PLI库子程序来编写自定义的系统任务。然而,Verilog 仿真器必须知道用户自定义系统任务和相应的用户自定义C函数的存在。这是通过把用户自定义系统任务连接到Verilog仿真器来实现的。

为了理解这个过程,以-个简单的系统任务$hello_verilog 为例进行说明。当$hello_verilog这个任务被调用时,它只是简单地输出一条消息“Helo Verilog World”。首先,实现该任务的C子程序必须用PLI库予程序定义。文件 hello_verilog.c中的子程序hello_verilog 如下所示

module hello—top

initial $hello_verilog;

endmodule3.内部数据的获取

在我们理解怎样使用PLI库子程序之前,首先需要理解在仿真器内部设计是如何表述的。每个模块被看做一组对象类型。对象类型是 Verilog 中定义的元素,例如:

模块实例、模块端口、模块的端到端路径以及模块之间的路径·顶层模块

原语实例和原语端口( terminal )

线网类型( net )、寄存器类型( register )、参数类型( parameter和specparam )整型、时间型和实型变量

时序检查

命名事件

4.PLI库子程序

PLI库子程序提供了对表示设计的内部数据结构进行存取的标准接口。为定义用户自己的系统任务而编写的用户自定义C子程序是用PLI库子程序编写的。在13.2 节的例子中,Shello._verilog是用户自定义系统任务,hello_verilog 是用户自定义C子程序,io_printf是PLI库子程序。

PLI库子程序有两大类:存取子程序和实用子程序。注意,vpi_子程序是存取子程序和实用子程序的扩展集合,未在本书中讨论。

学习时间:

提示:这里可以添加计划学习的时间

20230620

学习产出:

提示:这里统计学习计划的总量

PLI接口提供了一组C语吉接口子程序来读出、写入和提取设计的内部数据结构信息。设计者可以编写自己的系统任务来完成各种实用功能。

PLI接口可用于监视器、调试器、格式翻译器、延迟计算工具、自动激励生成器、转储文件生成器和其他实用工具。

用户自定义系统任务由相应的用户自定义C子程序实现。C子程序调用PLI库函数。

·通知仿真器把一个新的用户自定义系统任务与相应的用户C子程序联系起来的过程称为连接。仿真器不同,连接的过程也不相同。

用户自定义系统任务与标准的Verilog系统任务调用方式类似.例如$heilo_verilog()的调用与标准的系统任务调用一致。该用户自定义系统任务启动时,相应的用户自定义C子程序hello_verilog被执行。

在Verilog仿真器中,用多个对象集合组成的--个庞大数据结构来表示设计。可以通过PLI库子程序来存取内部数据结构。

存取子程序( acc)和实用子程序( tf)是两类PLI库子程序。

实用子程序代表了第一代 Verilog PLI。实用子程序用于在用户C子程序和原始Verilog 设计之间来回传输数据。

实用子程序以前缀tf_开头。实用子程序与对象处理互不影响。·存取子程序代表了第二代Verilog PLI。文章来源:https://www.toymoban.com/news/detail-513606.html

存取子程序可以读写设计的特定对象的信息。存取子程序以前缀acc_开头。存取子程序主要用在用户C子程序和内部数据表示的接口上。存取子程序与对象处理相互影响。

值变链接(VCL)是---类特殊的存取子程序,它们可以监视设计中的对象。当被监视的对象发生变化时,就执行最终用户子程序.文章来源地址https://www.toymoban.com/news/detail-513606.html

到了这里,关于FPGA基础知识-编程语言接口的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA] 7系列FPGA的基础知识](https://imgs.yssmx.com/Uploads/2024/02/484166-1.png)