步骤大致如下:1.根据逻辑电路图列出状态、驱动、输出方程

2.列出状态转移表

3.根据状态转移表画出状态转移图

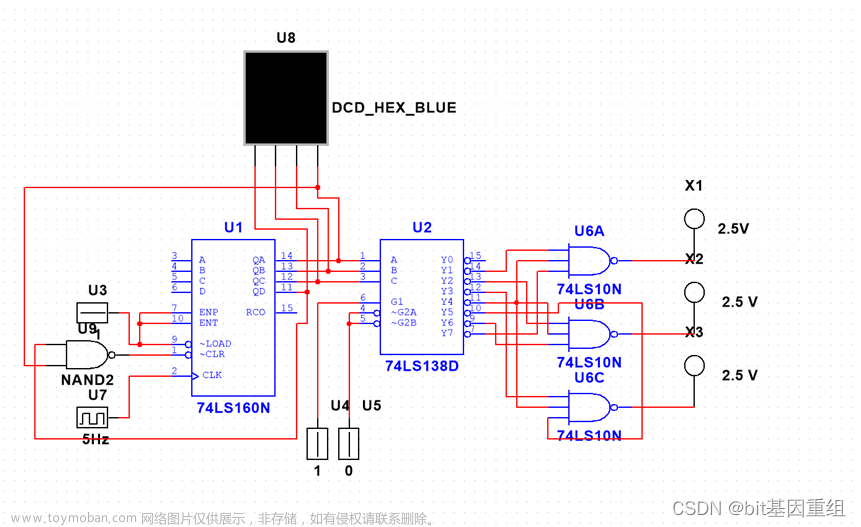

以以下逻辑电路图为例:

文章来源:https://www.toymoban.com/news/detail-513760.html

文章来源:https://www.toymoban.com/news/detail-513760.html

注意:状态转移图的由来以00到01为例,00表示Q2=0,Q1=0(注意状态转移图中Q2在前),将Q2=0,Q1=0,A=0代入驱动、状态和输出方程,得到新的Q2*=0,Q1*=1 ,Y=0。说明当A=0时,00状态得到了新的状态01(即Q2*=0,Q1*=1),所以有箭头从00状态指向01状态,而上面的0/0则表示/前的0表示代入方程时A的状态为0,/后的0表示代入方程后得到Y=0;以此类推,再将01状态(即Q2*=0,Q1*=1)代入新的方程得到新的状态和输出。还有刚刚只是代入了A=0的时候,接下来还要代入A=1的时候,又会得到新的状态和输出(11 1/1)。文章来源地址https://www.toymoban.com/news/detail-513760.html

到了这里,关于时序逻辑电路的状态转移图的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!