D触发器和与非门设计智力竞赛4人抢答电路,设有4个开关(S0~S3),另有4个指示灯,第一抢答者(第一个按下开关时)所对应的指示灯亮,其它三个开关任一个再按下时,其它三个指示灯也不会亮。

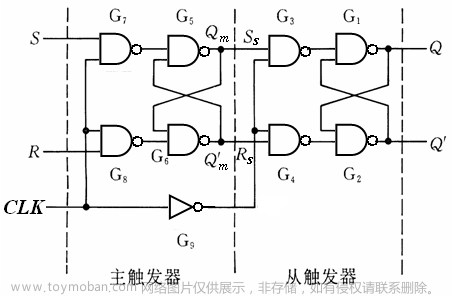

逻辑图

在抢答前,四人都处于高电位,抢答时按下按键,转化为低电位,产生下降沿脉冲信号,D触发器输出改变,指示灯亮。由于输入端被锁定,所有D触发器输出不再改变,所以只会有一盏灯亮。

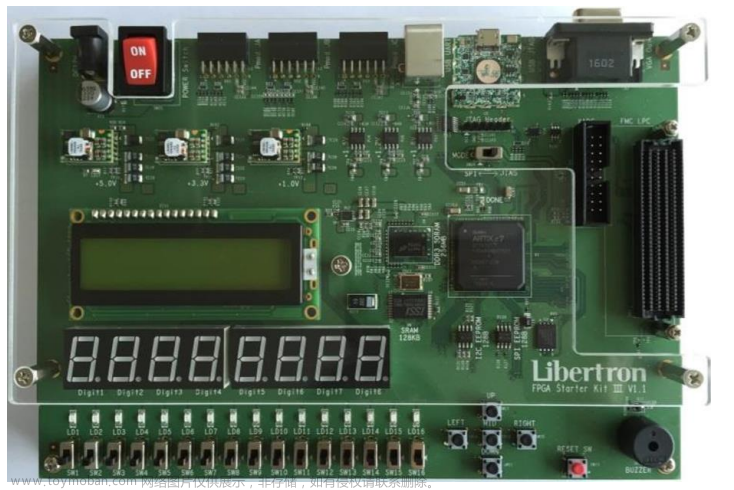

74LS000四2输入与非门 一片

74LS020双四输入与非门 一片

74LS74双上升沿D触发器 两片文章来源:https://www.toymoban.com/news/detail-514456.html

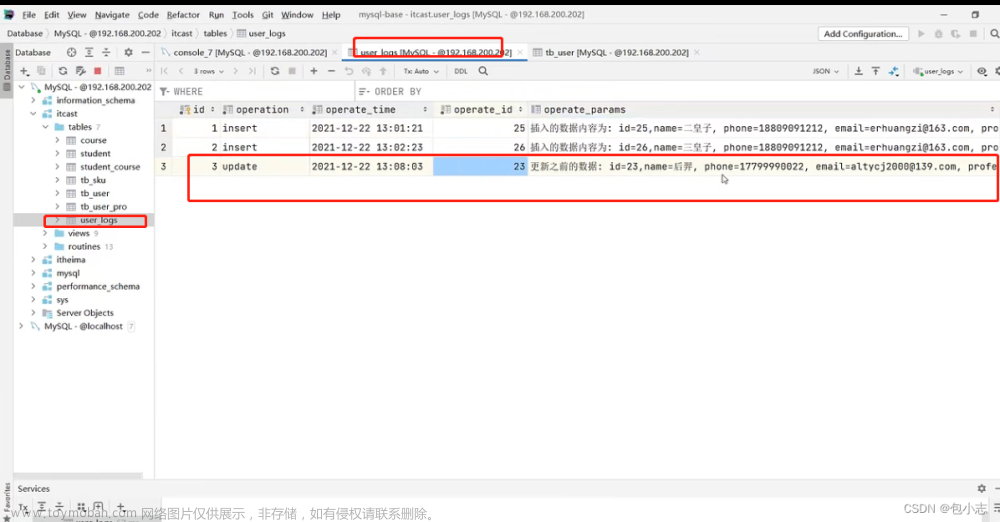

仿真链接:D触发器竞赛4人抢答电路multisim-单片机文档类资源-CSDN下载文章来源地址https://www.toymoban.com/news/detail-514456.html

到了这里,关于D触发器竞赛4人抢答电路的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!