目录

1位加法器

8位加法器

8位补码加减法器

32位补码加减法器

1位加法器

文章来源:https://www.toymoban.com/news/detail-514583.html

//

//创建日期:2022/09/21 19:05:50

//设计名称:一位加法器

//课程名称:adder_1

//说明:输入operand1,operand2和进位信号cin

// 输出当前位result和进位cout

//依赖项:

//

//版次:

//版本0.01-文件已创建

//其他注释:

//

//

module adder_1(operand1,operand2,cin,result,cout);

input operand1; // 加数1

input operand2; // 加数2

input cin; // 进位输入

output result; // 当前位输出

output cout; // 进位

wire c[3:0]; // 接线

// 当前位为三个输入的异或,三个输入为1的个数为奇数时,当前位为1

xor x1(c[0],operand1,operand2),

x2(result,c[0],cin);

// 进位信号为 与非(与非(输入1,输入2),与非(异或(输入1,输入2),进位))

nand na1(c[1],cin,c[0]),

na2(c[2],operand1,operand2),

na3(cout,c[1],c[2]);

endmodule

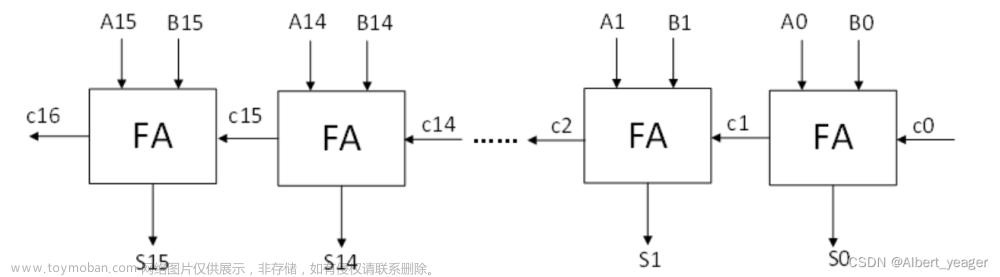

8位加法器

//

//创建日期:2022/09/21 19:05:50

//设计名称:8位加法器

//课程名称:adder_8

//说明:输入8位operand1,8位operand2和进位信号cin

// 输出8位result和进位cout

//依赖项:

// adder_1.v

//版次:

//版本0.01-文件已创建

//其他注释:

//

//

module adder_8(operand1,operand2,cin,result,cout);

input [7:0]operand1; // 加数1

input [7:0]operand2; // 加数2

input cin; // 进位输入

output [7:0]result; // 当前位输出

output cout; // 进位

wire [6:0] c; // 第 i 位的进位输入

adder_1 a0(operand1[0],operand2[0],cin,result[0],c[0]);

adder_1 a1(operand1[1],operand2[1],c[0],result[1],c[1]);

adder_1 a2(operand1[2],operand2[2],c[1],result[2],c[2]);

adder_1 a3(operand1[3],operand2[3],c[2],result[3],c[3]);

adder_1 a4(operand1[4],operand2[4],c[3],result[4],c[4]);

adder_1 a5(operand1[5],operand2[5],c[4],result[5],c[5]);

adder_1 a6(operand1[6],operand2[6],c[5],result[6],c[6]);

adder_1 a7(operand1[7],operand2[7],c[6],result[7],cout);

endmodule

8位补码加减法器

//

//创建日期:2022/09/21 19:05:50

//设计名称:8位补码加减法器

//课程名称:adder_subtract_8

//说明:输入8位operand1,8位operand2和加减信号add_or_sub(0+,1-)

// 输出8位result和溢出提示overflow

//依赖项:

// adder_1.v

//版次:

//版本0.01-文件已创建

//其他注释:

//

//

module adder_subtract_8(operand1,operand2,add_or_sub,result,overflow);

input [7:0]operand1; // 操作数1

input [7:0]operand2; // 操作数2

input add_or_sub; // 加减信号(0+,1-)

output [7:0]result; // 当前位输出

output overflow; // 溢出提示

wire [7:0] c; // 第 i 位的进位输入

wire [7:0] op2; // 操作数2的负数补码

// 由add_or_sub控制输入的是正数还是负数

xor x0(op2[0],add_or_sub,operand2[0]),

x1(op2[1],add_or_sub,operand2[1]),

x2(op2[2],add_or_sub,operand2[2]),

x3(op2[3],add_or_sub,operand2[3]),

x4(op2[4],add_or_sub,operand2[4]),

x5(op2[5],add_or_sub,operand2[5]),

x6(op2[6],add_or_sub,operand2[6]),

x7(op2[7],add_or_sub,operand2[7]);

// 加法器

adder_1 a0(operand1[0],op2[0],add_or_sub,result[0],c[0]);

adder_1 a1(operand1[1],op2[1],c[0],result[1],c[1]);

adder_1 a2(operand1[2],op2[2],c[1],result[2],c[2]);

adder_1 a3(operand1[3],op2[3],c[2],result[3],c[3]);

adder_1 a4(operand1[4],op2[4],c[3],result[4],c[4]);

adder_1 a5(operand1[5],op2[5],c[4],result[5],c[5]);

adder_1 a6(operand1[6],op2[6],c[5],result[6],c[6]);

adder_1 a7(operand1[7],op2[7],c[6],result[7],c[7]);

xor x8(overflow,c[6],c[7]);

endmodule

32位补码加减法器

//

//创建日期:2022/09/26 13:24:05

//设计名称:32位补码加减法器

//课程名称:adder_subtract_32

//说明:输入32位operand1,32位operand2和加减信号add_or_sub(0+,1-)

// 输出32位result和溢出提示overflow

//依赖项:

// adder_1.v

//版次:

//版本0.01-文件已创建

//其他注释:

//

//

module adder_subtract_32(operand1,operand2,add_or_sub,result,overflow);

input [31:0]operand1; // 操作数1

input [31:0]operand2; // 操作数2

input add_or_sub; // 加减信号(0+,1-)

output [31:0]result; // 当前位输出

output overflow; // 溢出提示

wire [31:0] c; // 第 i 位的进位输入

wire [31:0] op2; // 操作数2的负数补码

// 由add_or_sub控制输入的是正数还是负数

xor x0(op2[0],add_or_sub,operand2[0]),

x1(op2[1],add_or_sub,operand2[1]),

x2(op2[2],add_or_sub,operand2[2]),

x3(op2[3],add_or_sub,operand2[3]),

x4(op2[4],add_or_sub,operand2[4]),

x5(op2[5],add_or_sub,operand2[5]),

x6(op2[6],add_or_sub,operand2[6]),

x7(op2[7],add_or_sub,operand2[7]),

x8(op2[8],add_or_sub,operand2[8]),

x9(op2[9],add_or_sub,operand2[9]),

x10(op2[10],add_or_sub,operand2[10]),

x11(op2[11],add_or_sub,operand2[11]),

x12(op2[12],add_or_sub,operand2[12]),

x13(op2[13],add_or_sub,operand2[13]),

x14(op2[14],add_or_sub,operand2[14]),

x15(op2[15],add_or_sub,operand2[15]),

x16(op2[16],add_or_sub,operand2[16]),

x17(op2[17],add_or_sub,operand2[17]),

x18(op2[18],add_or_sub,operand2[18]),

x19(op2[19],add_or_sub,operand2[19]),

x20(op2[20],add_or_sub,operand2[20]),

x21(op2[21],add_or_sub,operand2[21]),

x22(op2[22],add_or_sub,operand2[22]),

x23(op2[23],add_or_sub,operand2[23]),

x24(op2[24],add_or_sub,operand2[24]),

x25(op2[25],add_or_sub,operand2[25]),

x26(op2[26],add_or_sub,operand2[26]),

x27(op2[27],add_or_sub,operand2[27]),

x28(op2[28],add_or_sub,operand2[28]),

x29(op2[29],add_or_sub,operand2[29]),

x30(op2[30],add_or_sub,operand2[30]),

x31(op2[31],add_or_sub,operand2[31]);

// 加法器

adder_1 a0(operand1[0],op2[0],add_or_sub,result[0],c[0]);

adder_1 a1(operand1[1],op2[1],c[0],result[1],c[1]);

adder_1 a2(operand1[2],op2[2],c[1],result[2],c[2]);

adder_1 a3(operand1[3],op2[3],c[2],result[3],c[3]);

adder_1 a4(operand1[4],op2[4],c[3],result[4],c[4]);

adder_1 a5(operand1[5],op2[5],c[4],result[5],c[5]);

adder_1 a6(operand1[6],op2[6],c[5],result[6],c[6]);

adder_1 a7(operand1[7],op2[7],c[6],result[7],c[7]);

adder_1 a8(operand1[8],op2[8],c[7],result[8],c[8]);

adder_1 a9(operand1[9],op2[9],c[8],result[9],c[9]);

adder_1 a10(operand1[10],op2[10],c[9],result[10],c[10]);

adder_1 a11(operand1[11],op2[11],c[10],result[11],c[11]);

adder_1 a12(operand1[12],op2[12],c[11],result[12],c[12]);

adder_1 a13(operand1[13],op2[13],c[12],result[13],c[13]);

adder_1 a14(operand1[14],op2[14],c[13],result[14],c[14]);

adder_1 a15(operand1[15],op2[15],c[14],result[15],c[15]);

adder_1 a16(operand1[16],op2[16],c[15],result[16],c[16]);

adder_1 a17(operand1[17],op2[17],c[16],result[17],c[17]);

adder_1 a18(operand1[18],op2[18],c[17],result[18],c[18]);

adder_1 a19(operand1[19],op2[19],c[18],result[19],c[19]);

adder_1 a20(operand1[20],op2[20],c[19],result[20],c[20]);

adder_1 a21(operand1[21],op2[21],c[20],result[21],c[21]);

adder_1 a22(operand1[22],op2[22],c[21],result[22],c[22]);

adder_1 a23(operand1[23],op2[23],c[22],result[23],c[23]);

adder_1 a24(operand1[24],op2[24],c[23],result[24],c[24]);

adder_1 a25(operand1[25],op2[25],c[24],result[25],c[25]);

adder_1 a26(operand1[26],op2[26],c[25],result[26],c[26]);

adder_1 a27(operand1[27],op2[27],c[26],result[27],c[27]);

adder_1 a28(operand1[28],op2[28],c[27],result[28],c[28]);

adder_1 a29(operand1[29],op2[29],c[28],result[29],c[29]);

adder_1 a30(operand1[30],op2[30],c[29],result[30],c[30]);

adder_1 a31(operand1[31],op2[31],c[30],result[31],c[31]);

xor x32(overflow,c[31],c[30]);

endmodule8位加减法器仿真

`timescale 1ns / 1ps

//

//创建日期:2022/09/21 20:19:20

//设计名称:8位补码加减法器测试

//课程名称:testbench

//说明:输入8位operand1,8位operand2和加减信号add_or_sub(0+,1-)

// 输出8位result和溢出提示overflow

//依赖项:

// adder_1.v

// adder_subtract_8

//版次:

//版本0.01-文件已创建

//其他注释:

//

//

module testbench;

reg [7:0] input_1; // 加数 1

reg [7:0] input_2; // 加数 2

reg add_or_sub; // 加减信号(0+,1-)

wire [7:0] output_1; // 输出

wire overflow; // 溢出提示

//调用adder_subtract_8模块

adder_subtract_8 uut(

.operand1(input_1), // 加数1

.operand2(input_2), // 加数2

.add_or_sub(add_or_sub), // 加减信号(0+,1-)

.result(output_1), // 当前位输出

.overflow(overflow) //溢出提示

);

//初始化仿真

initial begin

// Initialize Inputs

input_1 = 0;

input_2 = 0;

add_or_sub = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

always #10 input_1 = $random; //$random为系统任务,产生一个随机的8位数

always #10 input_2 = $random; //#10 表示等待10个单位时间(10ns),即每过10ns,赋值一个随机的32位数

always #10 add_or_sub = {$random} % 2; //加了拼接符,{$random}产生一个非负数,除2取余得到0或1

endmodule

结果示例,32位太多了,8位好算

文章来源地址https://www.toymoban.com/news/detail-514583.html

文章来源地址https://www.toymoban.com/news/detail-514583.html

到了这里,关于Verilog 加法器/减法器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA]用Verilog写一个简单三位二进制加法器和减法器](https://imgs.yssmx.com/Uploads/2024/02/761556-1.png)