使用 for语句实现,后续继续做并行优化…

最近需要用 verilog写一个矩阵乘法的简单模块,本来想着网上随便搜一个复制粘贴一下,却发现居然找不到有源码的(好多还上传到了CSDN资源),罢了罢了,照着Github的自己写一个吧。

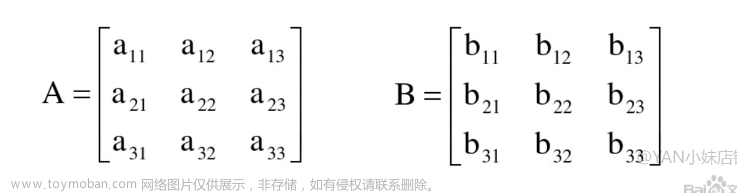

我写的是 3 * 3 的、数值位宽为 [3:0] (0-15)的矩阵乘法,你完全可以根据你的板子资源加以更改:文章来源:https://www.toymoban.com/news/detail-515111.html

Verilog代码

`timescale 1ns / 1ps

module mm(A,B,Result);

input [35:0] A; // 行*列*数据位宽 3*3*4

input [35:0] B;

output [89:0] Result; // 行*列*数据位宽 3*3*10,

reg [71:0] Result;

reg [3:0] A1 [0:2][0:2];

reg [3:0] B1 [0:2][0:2];

reg [9:0] Res1 [0:2][0:2]; // 因为A和B相乘最大的值为15*15=225,所以数据位宽为225*3=10位(一行乘一列)

integer i,j,k;

always@ (A or B)

begin

// 一维矩阵转为二维矩阵

{A1[0][0],A1[0][1],A1[0][2],A1[1][0],A1[1][1],A1[1][2],A1[2][0],A1[2][1],A1[2][2]} = A;

{B1[0][0],B1[0][1],B1[0][2],B1[1][0],B1[1][1],B1[1][2],B1[2][0],B1[2][1],B1[2][2]} = B;

{Res1[0][0],Res1[0][1],Res1[0][2],Res1[1][0],Res1[1][1],Res1[1][2],Res1[2][0],Res1[2][1],Res1[2][2]} = 71'd0;

i=0; j=0; k=0;

for(i=0;i<3;i=i+1)

begin

for(j=0;j<3;j=j+1)

begin

for(k=0;k<3;k=k+1)

begin

Res1[i][j]=Res1[i][j]+ (A1[i][k]*B1[k][j]);

end

end

end

Result = {Res1[0][0],Res1[0][1],Res1[0][2],Res1[1][0],Res1[1][1],Res1[1][2],Res1[2][0],Res1[2][1],Res1[2][2]};

end

endmodule

Testbench

`timescale 1ns / 1ps

module test_bench;

reg [35:0] A;

reg [35:0] B;

wire [71:0] Answer;

Calculator calculator(.A(A), .B(B), .Result(Answer));

initial begin

//Initial inputs

A={4'd1,4'd2,4'd3,4'd4,4'd5,4'd6,4'd7,4'd8,4'd9};

B={4'd5,4'd3,4'd5,4'd8,4'd6,4'd10,4'd5,4'd3,4'd0};

end

// VCS联合Verdi查看波形,使用自带的波形查看器可删除这段代码

`ifdef FSDB

initial begin

$fsdbDumpfile("tb_mm.fsdb");

$fsdbDumpvars;

end

`endif

endmodule

仿真和结果验证

手动计算验证一下(我这里数据少就手算了,建议你们写个脚本验证):

Ok,没有问题,后续继续优化,用并行计算的方式实现。文章来源地址https://www.toymoban.com/news/detail-515111.html

到了这里,关于FPGA | Verilog 实现矩阵乘法(附源码)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!