-

首先参考这篇博客完成FPGA的硬件固化

-

参考arm官方文档发现直接导入hex不能使用,开始转向文档中提到的第二个方法

-

-

-

发现这篇博客满足要求

-

下面进行第二篇博客的细节补充

-

修改mmi文件

找到元件名字

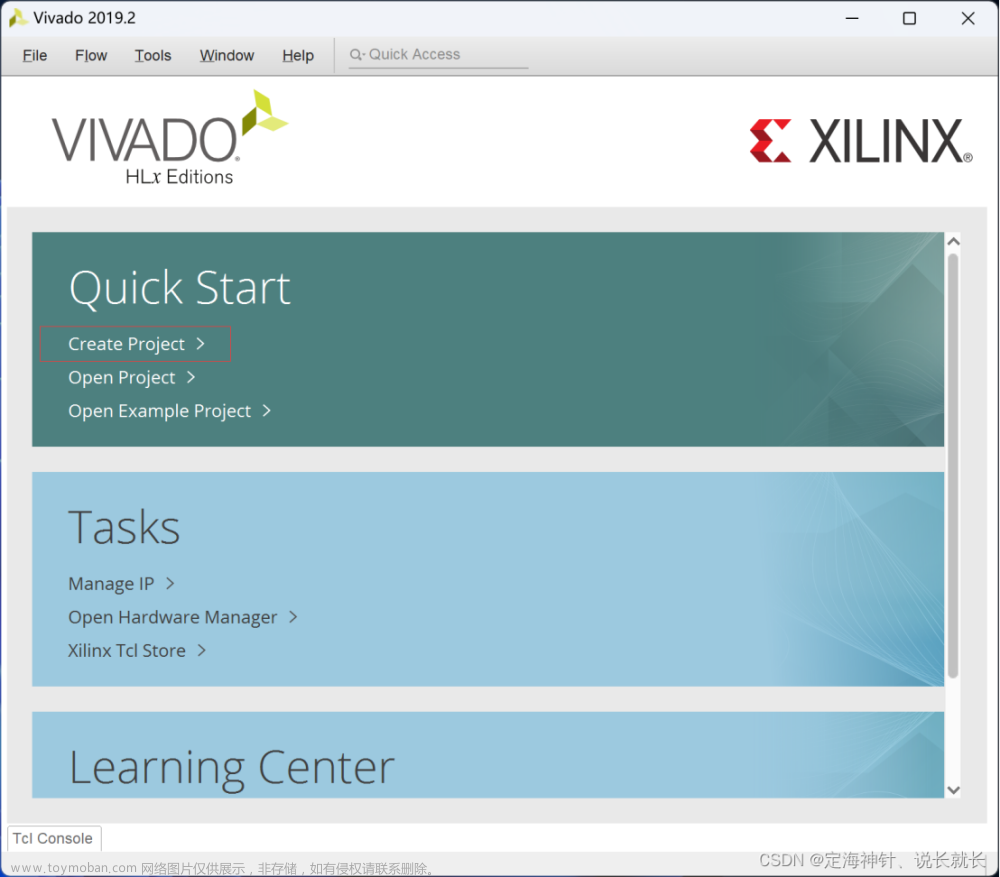

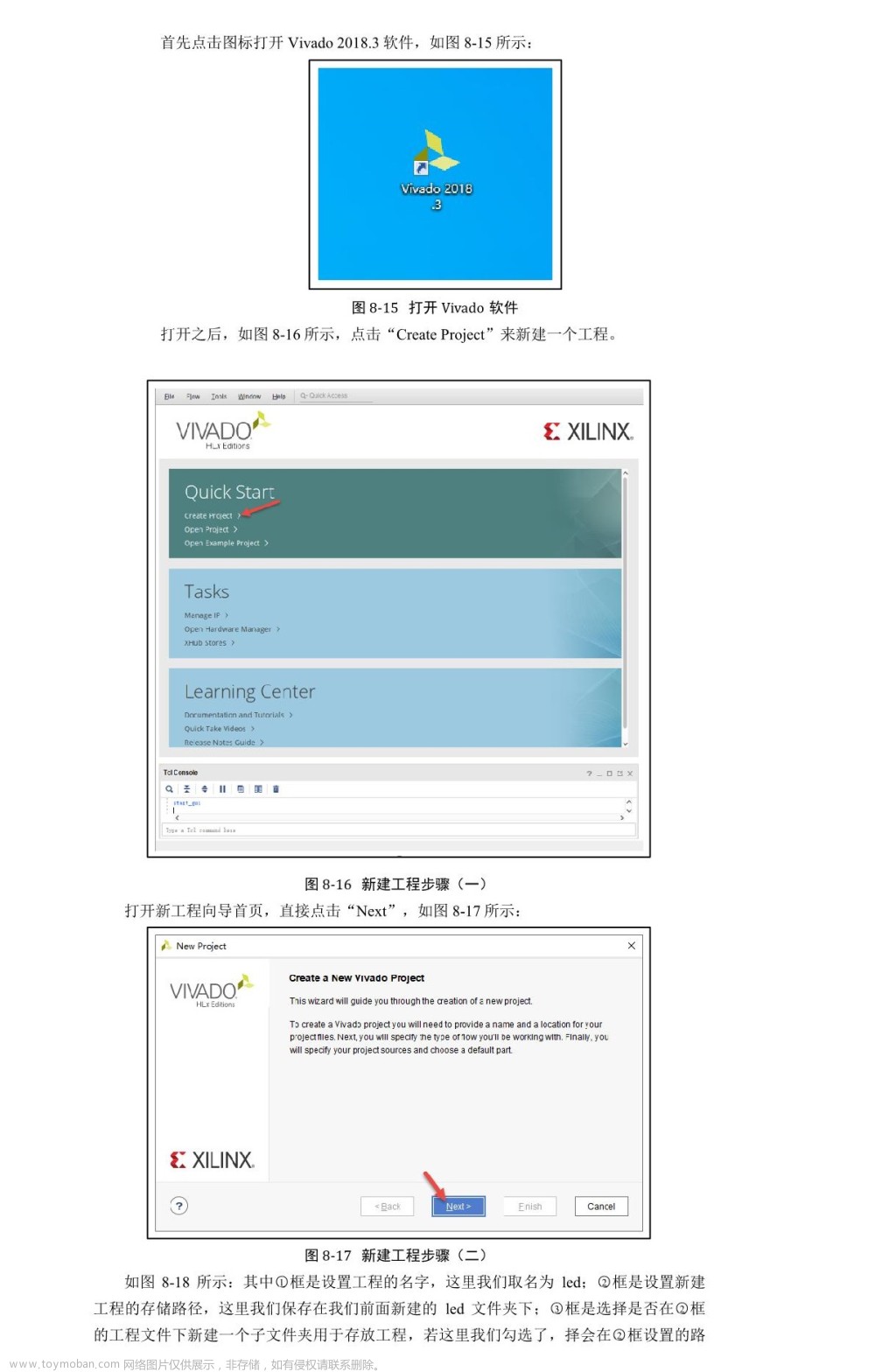

打开FPGA工程的实现

融合bit文件

生成完 mcs文件后 直接打开 文章来源:https://www.toymoban.com/news/detail-515543.html

文章来源:https://www.toymoban.com/news/detail-515543.html

然后就完成软件和硬件的固化啦!文章来源地址https://www.toymoban.com/news/detail-515543.html

到了这里,关于FPGA 固化 硬件底层和软件hex代码 基于vivado和keil的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!