1.建立工程,在建立工程的第四步中的Simulation下选择Tool Name为ModelSim-Altera,再在后面的Format(s)中选择Verilog HDL。继续构建完工程;

2.在工程中写好程序,保存并编译,确定没有错误后进行下一步;

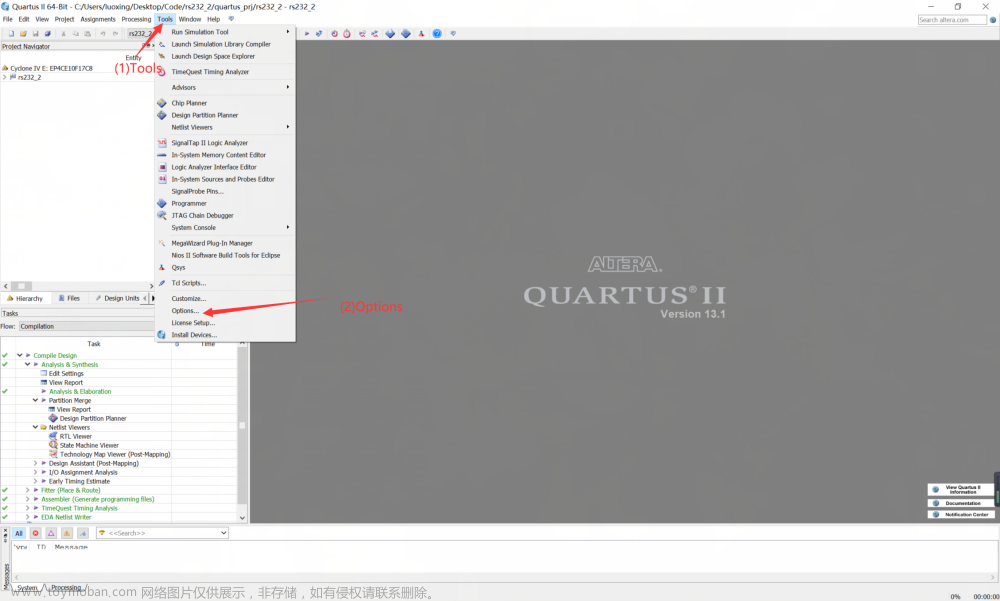

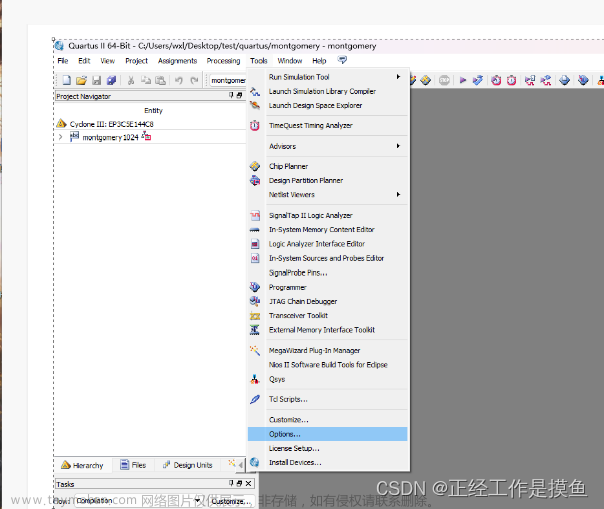

3.选择Tools菜单中的Options,在General中选择EDA Tool Options,在右边的列表中有ModelSim-Altera一栏,点击后面的省略号选择ModelSim所安装的位置,注意后面两项modelsim_ase、win32aloem这两项是相同的,前面的可能会根据安装位置不同而不同,请找到自己电脑安装ModelSim的位置进行选择;

4.选择Assignments菜单中的settings,在左侧的EDA Tool Settings中选择Simulation,如果按照1中设置,这里如图中所示,如果没有1中的设置,在这里将红框中的内容进行更改。

5.选择Processing菜单中的Start,单击Start菜单中Start Test Bench Template Writer。会生成一个.vt文件,接下来选择File菜单下的Open,选择simulation文件夹→ modelsim文件夹,在里面选择文件类型为.vt的文件,打开后将程序中module后的代码复制,如本例中为红框内。

6.再次按照4中操作,这一次将下面的Compile test bench选中,点击后面的Test Benches,点击New,在弹出的窗口中的Test bench name中粘贴5中复制的内容,在下面File name点击后面的省略号,选择5中生成的.vt文件。点击Add,OK。

7.选择Tools菜单,选择Run EDA Simulation Tool→EDA RTL Simulation进行仿真。文章来源:https://www.toymoban.com/news/detail-515633.html

文章来源地址https://www.toymoban.com/news/detail-515633.html

文章来源地址https://www.toymoban.com/news/detail-515633.html

到了这里,关于Quartus调用ModelSim进行仿真的步骤的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!