“found timing loop”概述

found timing loop出现在critical warning警告中,是不可忽略的警告,如果found timing loop不消除,代码最终将无法执行。found timing loop通常是在模块例化过程中将同一模块的input与output直接相连;或者是由于模块中的组合逻辑形成了latch。

“found timing loop”警告的位置查找方法

(1)查阅message

“found timing loop”无法通过message、log等查阅,也不会提示代码位置,但会提示所在模块。以下图举例

在上图模块中,出现了29个 “found timing loop”警告,且在ZYNQ_Write文件中。

(2)查阅时序检查报告(synthesis->Report Timing Summary)

点击Report Timing Summary

文章来源地址https://www.toymoban.com/news/detail-515853.html

点击OK

运行中

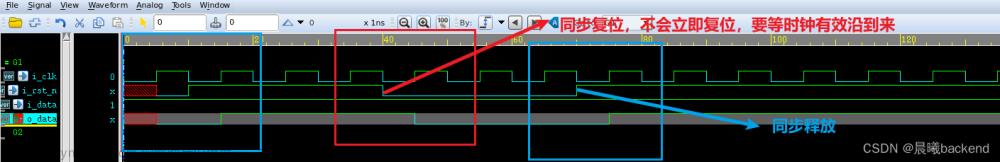

在loops中可以看到警告相关的寄存器(但可能不仅仅是寄存器引起的loop,也有可能是状态机逻辑错误引起的loop或者latch)

通过schematic查看具体模块

文章来源:https://www.toymoban.com/news/detail-515853.html

文章来源:https://www.toymoban.com/news/detail-515853.html

到了这里,关于Verilog综合(synthesis)过程中出现 found timing loop.的critical warning的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!