目录

存储器芯片与CPU的连接

典例

典例二

主存储器容量的扩展与连接方法

位拓展

字拓展

例题

主存大小计算

总结:

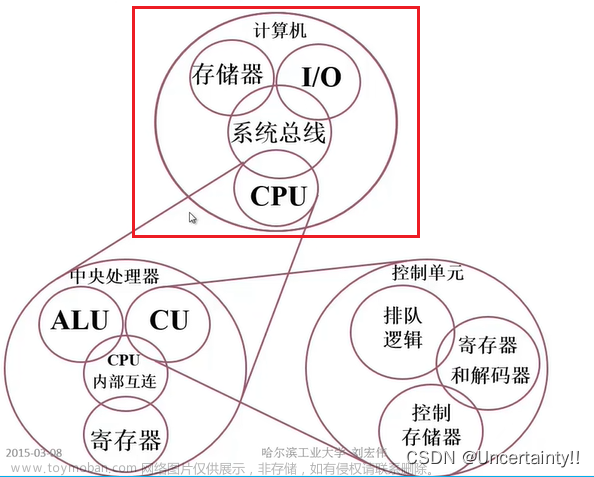

存储器芯片与CPU的连接

1. 确定所需芯片的数量(可以通过计算得出)

2. 确定每个芯片的分配地址 (区分最大地址还是最小地址,容量)

3. 确定每个芯片片选信号CS的产生方式 (3-8译码器或者4-16译码器选择使用哪一片存储芯片)

4. 完成CPU与存储芯片的连接:

地址线(决定CPU访存: 空间的大小【相当于多少个的单元】) (Ax-A0)

数据线(决定访存单元的大小)(Dx-D0)

读/写(R/W#,只有SRAM可读可写,不用连ROM)

控制线 (MREQ#,一般连上译码器,控制译码器的启动从而控制存储芯片的工作)

典例

设CPU有16根地址线,8根数据线,并用MREQ#作访存控 制信号(低电平有效),用R/W#作读/写控制信号(高 电平为读,低电平为写)。

现有下列存储芯片:1K*4 位SRAM;4K*8位SRAM;8K*8位SRAM;2K*8位ROM;4K*8 位ROM;8K*8位ROM;及3:8译码器和各种门电路。

要求:主存的地址空间满足下述条件:最小8K地址为 系统程序区(ROM区),与其相邻的16K地址为用户程序区(RAM区),最大4K地址空间为系统程序区(ROM 区)。

请画出存储芯片的片选逻辑,存储芯片的种类、片数

画出CPU与存储器的连接图。

解: 先分析选择的地址大小

上面这一个部分需要存储容量计算的问题,我放到文章后面自行学习;

第二步:选择芯片

最小8K系统程序区←8K*8位ROM,1片

16K用户程序区←8K*8位SRAM, 2片;

4K系统程序工作区←4K*8位ROM,1片。

第三步,分配CPU地址线。

CPU的低13位地址线A12~A0与1片8K*8位ROM和两片 8K*8位SRAM芯片提供的地址线相连;

将CPU的低12 位地址线A11~A0与1片4K*8位ROM芯片提供的地址线相连。

第四步,译码产生片选信号。

典例二

某机字长 16 位,CPU 地址总线 18 位,数据总线 16 位,存储器按字编址,CPU 的 控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号, 高电平为读信号)。已知该机已有 8K×16 位的 ROM 存储器,地址处于主存的最高端;现在再用若干个 16K×8 位的 SRAM 芯片形成 128K×16 位的 RAM 存储区域,起始地址为 00000H,假设 SRAM 芯片有 CS#(片选,低电平有效)和 WE#(写使能,低电平有效)信号控制端;试 写出RAM、ROM 的地址范围,并画出 SRAM、ROM 与 CPU 的连接图,请标明 SRAM 芯片个数、译码器的输入输出线、地址线、数据线、控制线及其连接。

主存储器容量的扩展与连接方法

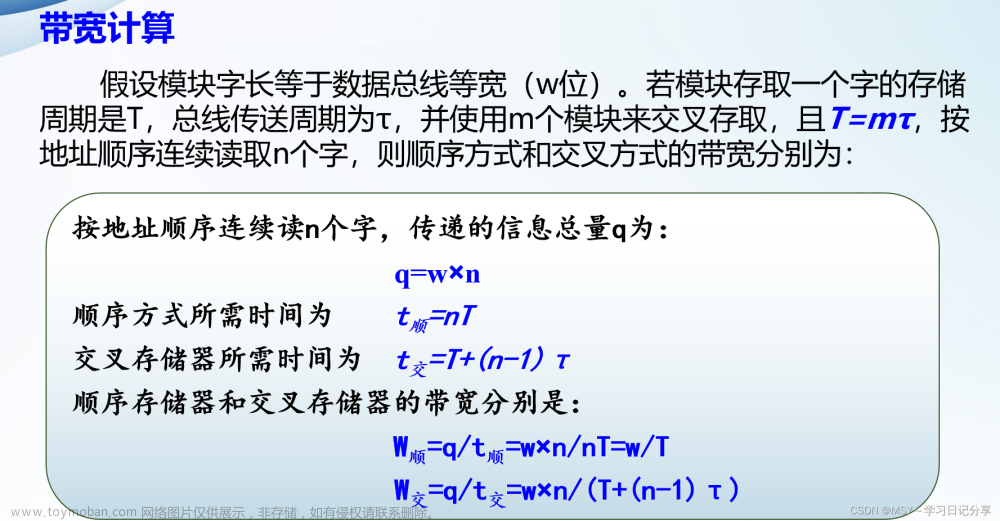

扩展主存容量的方法:位扩展、字扩展和字位同时扩展

位拓展

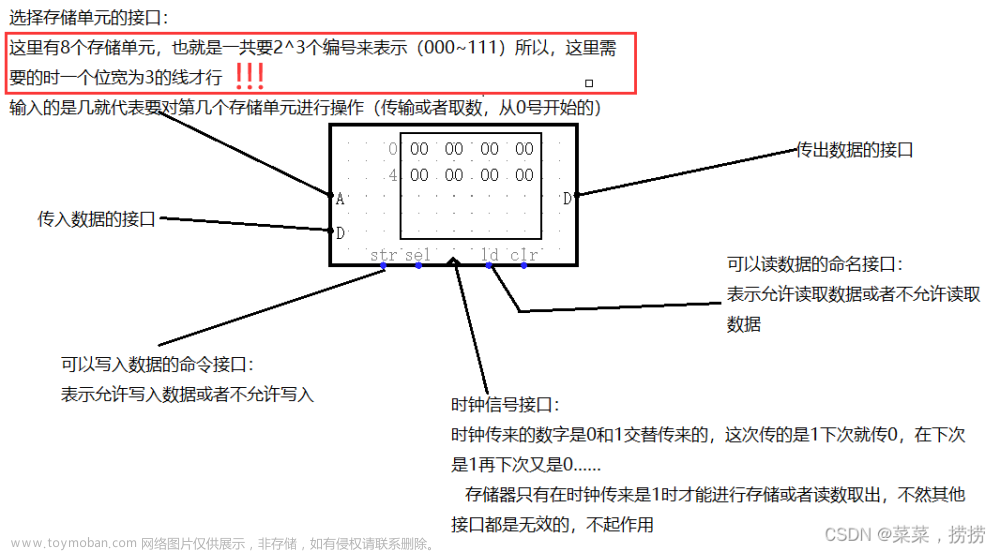

我的理解:位拓展是把每一个存储芯片容量以及输出输出都变大,然后就实现了存储大小的拓展

字拓展就是通过增加地址线从而增加多个存储芯片,这样也实现了存储大小的拓展

我们先来看位拓展,下面这个图已经很生动形象了~

一般做题画图时,都是把两个存储芯片叠在一起画,然后要注意输出到Dx-D0的箭头位数要增大

字拓展

字拓展就是通过增加地址线从而增加多个存储芯片,这样也实现了存储大小的拓展,一般来说是连多个芯片 (字扩展的芯片是互斥工作方式,每次访问时只有一个芯片工作)

例题

用4K*8位芯片构建CPU的16K*8位的存储空间

解:

所需芯片个数:(16K*8)/(4K*8)=4(片)

字扩展的4个芯片是互斥工作方式,每次访问时只有一个芯片工作

芯片内4K个单元---4K个地址---12位二进制编码表示:全0~全1

CPU访问某个单元时送出的地址是14位,多出的高2位地址用来决定选择哪个芯片,剩下的12位地址在芯片内译码选择某个单元

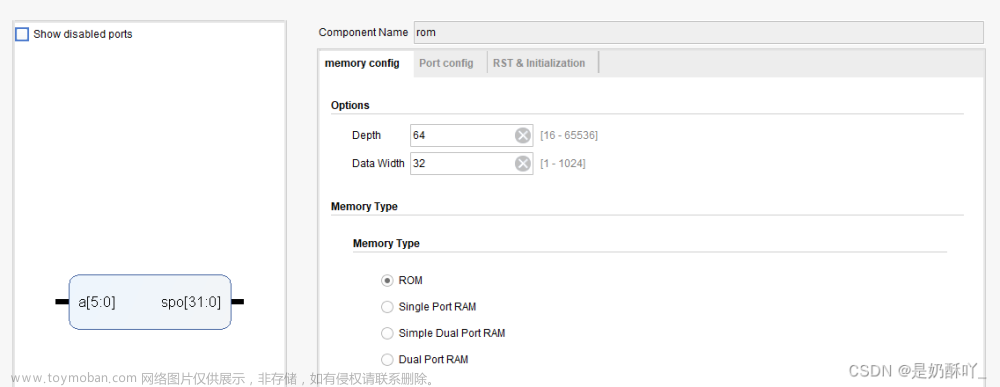

主存大小计算

记住最小存储单元是字节,所以我们要清楚后面cache的多少位和字节的转换,单位统一;

一个字节=8位;1KB=2^10个单元

总结:

一定一定要记住,2^30=1G, 2^20=1M, 512KB=2^19.

8KB=2^13==(A12-A0【记住A0占一位。。】)

片选CS等等题目会给,要看清楚译码器输出与输入是低有效还是高有效,对片选信号很重要。。

ROM芯片没有R/W#信号!!

MERQ#

注意每一个芯片地址线的位数!CPU输出的时候很容易出错,要选择好或门、与门文章来源:https://www.toymoban.com/news/detail-515860.html

最大(高)地址空间【从1111……开始反向】,和最低(小)地址空间【从000……开始正向】文章来源地址https://www.toymoban.com/news/detail-515860.html

到了这里,关于计算机组成原理第五章----存储器容量的扩展与芯片连接的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!