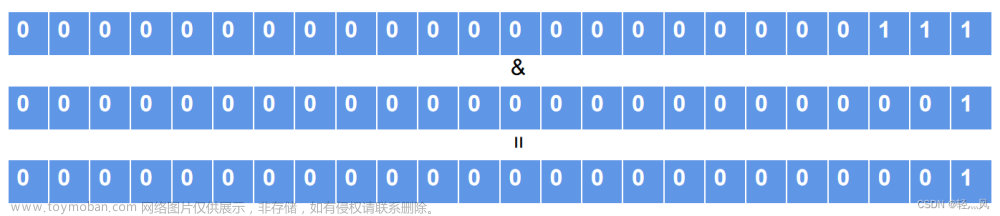

如图所示,先看原理。1110_1010对应的十进制是3位,所以bcd码有12位。先12位bcd全部取0,然后二进制码左移一位,从个位开始判断是否大于4,不大于4继续左移。大于4就加3(0011),然后再左移一位,然后再进行判断,直至所有二进制码全部左移完。

框图如下

框图如下

这里输入的二进制码是20位,对应十进制是6位,bcd码也就是24位。 输出是个位,十位直到十万位总共6个输出。

下面是波形图,data_shift是暂时存放输入的data和24位bcd码,合计44位。shift_flag一个周期内低电平进行判断运算,高电平进行移位运算,一个周期处理一位数据。这里22位一个周期的原因是最头0是赋初值,1-20是对应20位数据。21是末尾取值。

文章来源:https://www.toymoban.com/news/detail-516594.html

文章来源:https://www.toymoban.com/news/detail-516594.html

下面是verilog代码文章来源地址https://www.toymoban.com/news/detail-516594.html

module bcd_8421

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire [19:0] data 到了这里,关于FPGA自学之路12(二进制转换8421bcd码)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!