简答

22. 什么是存储器刷新?常用哪几种方式?

为了维护所存信息,需要在一定时间内将所存的信息读出再重新写入,这一过程称为刷新。刷新是一行一行进行的,由CPU自动完成。

主要有:可集中刷新,分散刷新和异步刷新

32. 四地址格式指令、三地址格式指令、二地址格式指令分别需要访问几次内存?

如果地址字段均指示主存的地址,则四地址格式指令完成一次指令需要访问四次内存(取指令一次,取两个操作数两次,存放结果一次)

三地址格式指令也要访问四次内存,二地址格式访问三次内存

44. 存取周期和存取时间的区别。

①主体不同:存取时间是CPU读或写内存内数据的过程时间,存取周期是连续启动两次独立的读或写操作

②原理不同:存取时间从CPU发出指令给内存时,便会要求内存取用特定地址的数据,内存响应CPU后便会将CPU所需要的数据送给CPU,一直到CPU收到数据为止

存取周期将存储单元与存储寄存器之间进行读写。存储器从接受读出命令到被读出信息稳定在MDR的输出端为止的时间间隔

③代表含义不同。存取时间:用它的倒数来代表速度

存取周期:为存储器的性能指标之一,直接影响电子计算机的技术性能

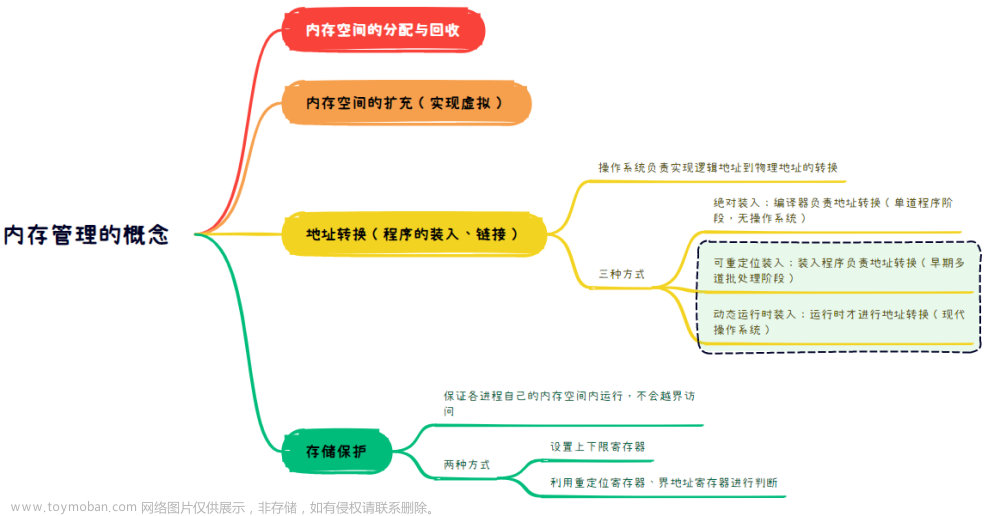

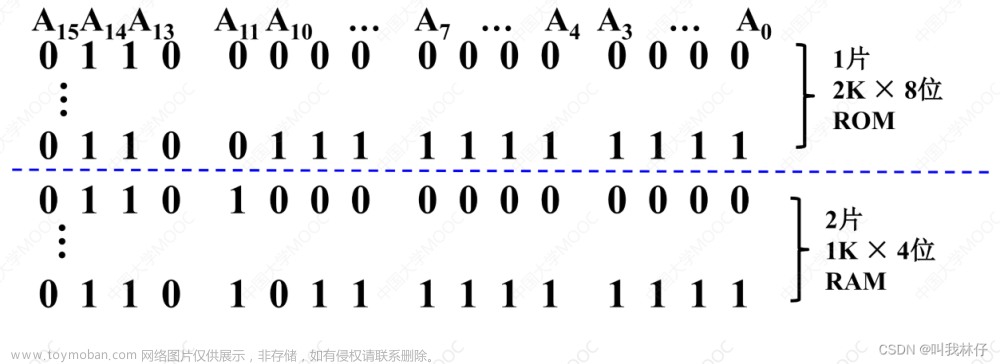

48. ROM 和 RAM 的基本概念

ROM是只读存储器,在存储过程中只能读出信息不能写入信息。

RAM是随机存取存储器,在程序执行的过程中既可写入信息又可读出信息

51. 多重中断是指:在 CPU 执行某个中断服务程序的过程中,产生了优先级更高

的中断请求,CPU 暂停现行中断服务程序的执行,转去处理该事件的中断,

处理完后返回现行中断服务程序继续执行的过程;实现多重中断的必要条件:

在现行中断服务期间,中断允许触发器为 1,即处于开中断状态。

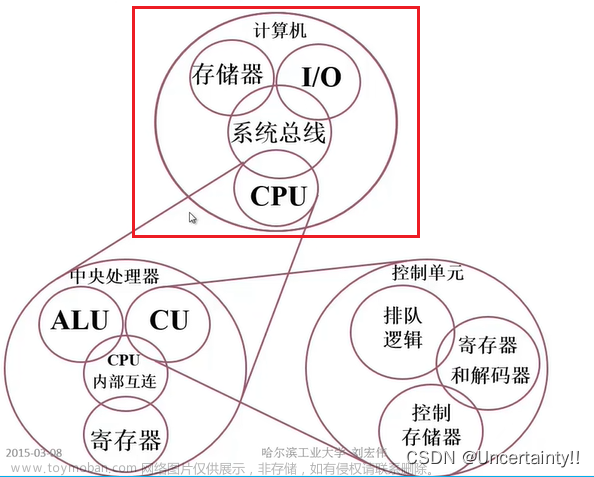

52. 简述冯诺依曼计算机的特点。

计算机由运算器,存储器,控制器,输入设备,输出设备组成,指令和数据以同等地位存放于存储器内,并可按地址寻访,指令和数据均按二进制数表示,指令由操作码和地址码组成,

指令在存储器内按顺序存放,机器以运算器为中心

53. 总线的概念和分类。

总线是连接各个部位的信息传输线,是各部位共享的传输介质

分类:片内总线,系统总线,通信总线

54. 为什么要设置总线的判优控制?常见的集中式总线控制有几种?

为了解决多个部件同时申请总线时的使用权分配问题

链式查询,计数器查询,和独立请求

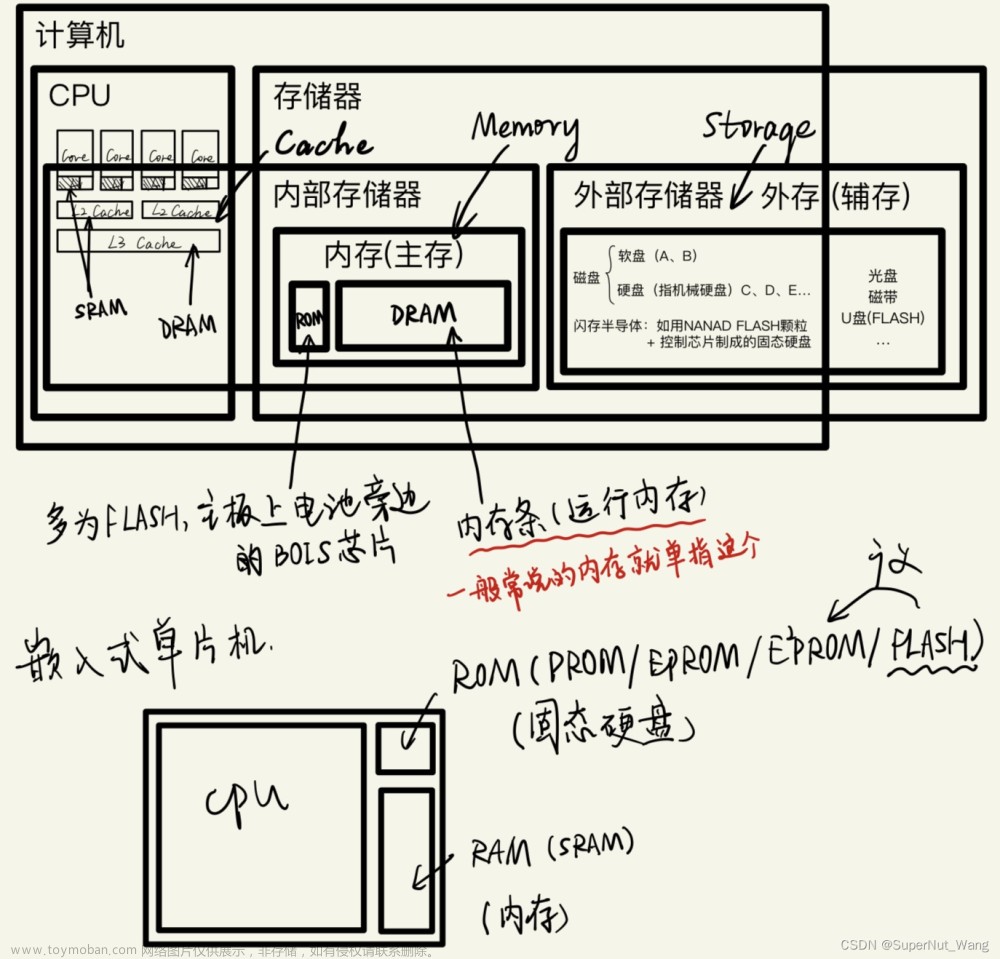

55. 存储器的层次结构主要体现在什么地方?为什么要分这些层次?

主要体现在Cache-主存和主存-辅存这两个存储层次上

Cache-主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。

综合上述两个存储层次的作用,从整个存储系统来看,就达到了速度快、容量大、位价低的优化效果。

56. 什么叫寻址方式?常用的寻址方式有哪些呢?

寻址方式是指寻找指令中操作数所在地址的方法

常用的有:立即寻址,直接寻址,寄存器寻址,寄存器间接寻址,变址寻址等

57. 请简述高速缓冲存储器(Cache)在计算机系统中所起的作用。

解决主存与CPU速度的不匹配问题,可以使CPU不直接访问主存,而与高速cache直接交换信息

58. 请简述 CPU 在计算机中的功能。

1取指令。控制器必须具备能自动地从存储器中取出指令的功能

2分析指令 (1)分析此指令要完成什么操作(2)分析参与此次操作的操作数地址,即操作数的有效地址

3执行指令 根据分析指令产生的操作命令和操作数地址的要求,形成操作控制信号序列,通过对运算器、存储器以及I/O设备的操作,执行每条指令

59. 什么是中断?简单归纳中断处理过程。

中断:计算机在执行的过程中,当出现异常情况或特殊请求时,计算机停止现行程序的运行,转向对这些异常情况或特殊请求的处理,处理结束后再返回到现行程序的间断处,继续执行原程序

五个过程①中断请求②中断判优③中断响应④中断服务⑤中断返回

71. 简述 MAR、MDR、PC、IR 的含义与作用。

MAR:存储地址寄存器,用于存放将被访问的存储单元的地址

MDR:存储器数据寄存器。用于存放欲存入存储器中的数据或最近从存储器中读出的数据

PC:程序计数器,存放现行指令的地址,通常具有计数功能。当遇到转移类指令时,PC的值可被修改

IR:指令寄存器,存放当前欲执行的指令

72. 理解 JMP、SKP、STA、LDA 等常见指令的含义。文章来源地址https://www.toymoban.com/news/detail-517123.html

文章来源:https://www.toymoban.com/news/detail-517123.html

到了这里,关于什么是存储器刷新的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[深入理解NAND Flash (原理篇)] Flash(闪存)存储器底层原理 | 闪存存储器重要参数](https://imgs.yssmx.com/Uploads/2024/02/735174-1.png)