前言

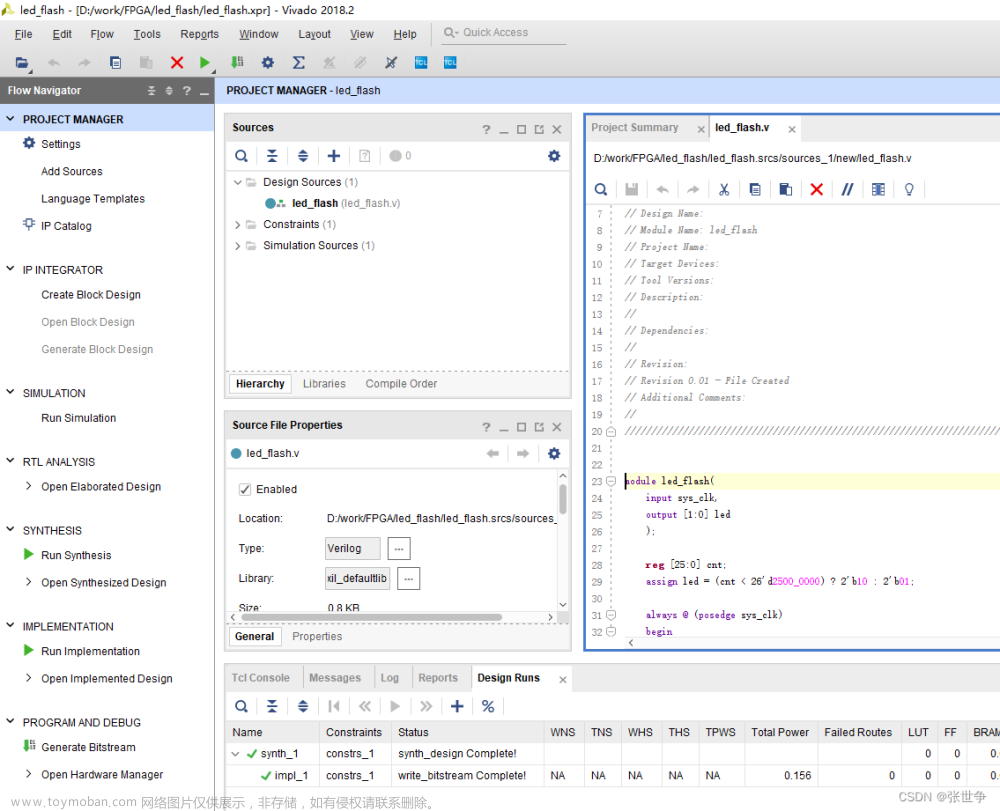

- Vivado 2018.2,配置好 MicroBlaze Uartlite等Block Design后,生成了 bin、bin文件,此时烧写到FPGA板子上,发现没有任何动静,所以需要 SDK的支持

导出 Hardware

-

这里使用的Vivado 2018.2,最新的 Vivado版本,如 Vivado 2020.2,启动的SDK 是 :Vitis,启动方式稍微有点不同,后面补充 Vivado 2020.2版本的操作方法

-

【File】-> 【Export】 -> 【Export Hardware…】,导出FPGA 的硬件设计文件

文章来源:https://www.toymoban.com/news/detail-517988.html

文章来源:https://www.toymoban.com/news/detail-517988.html

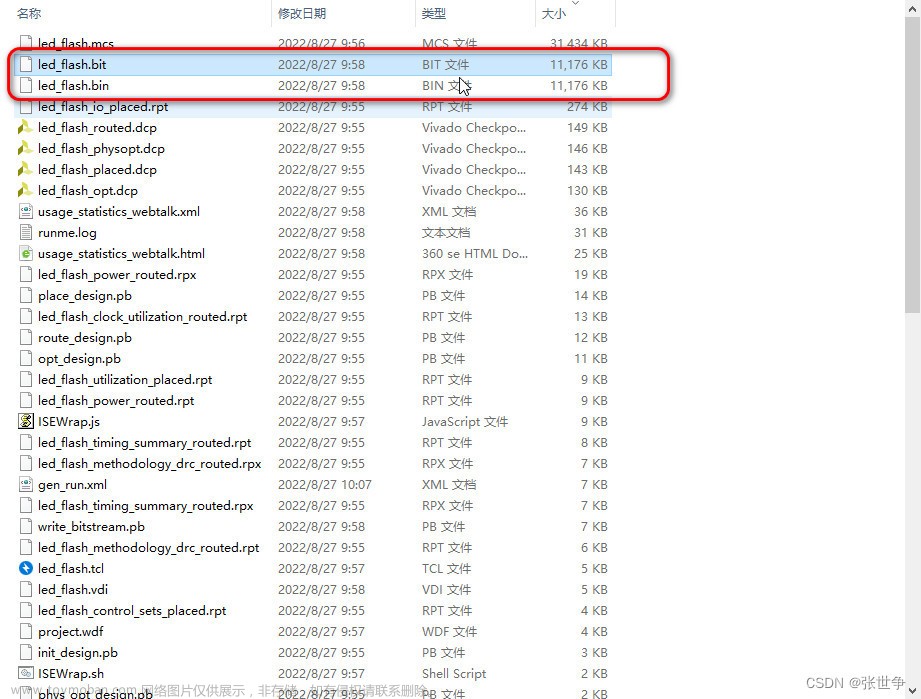

- 这里勾选【Include bitstream】文件,方便 Xilinx SDK 中下载FPGA程序

文章来源地址https://www.toymoban.com/news/detail-517988.html

文章来源地址https://www.toymoban.com/news/detail-517988.html

- 如果不更改目录,默认导出到了 .sdk 目录,所以导出目录不更改的话,每次导出,都会覆盖之前的导出文件,这里可以更改之前导出的 .sdk 目录,保存设计备份

到了这里,关于FPGA 学习笔记:Vivado 2018.2 MicroBlaze 启动 SDK的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!