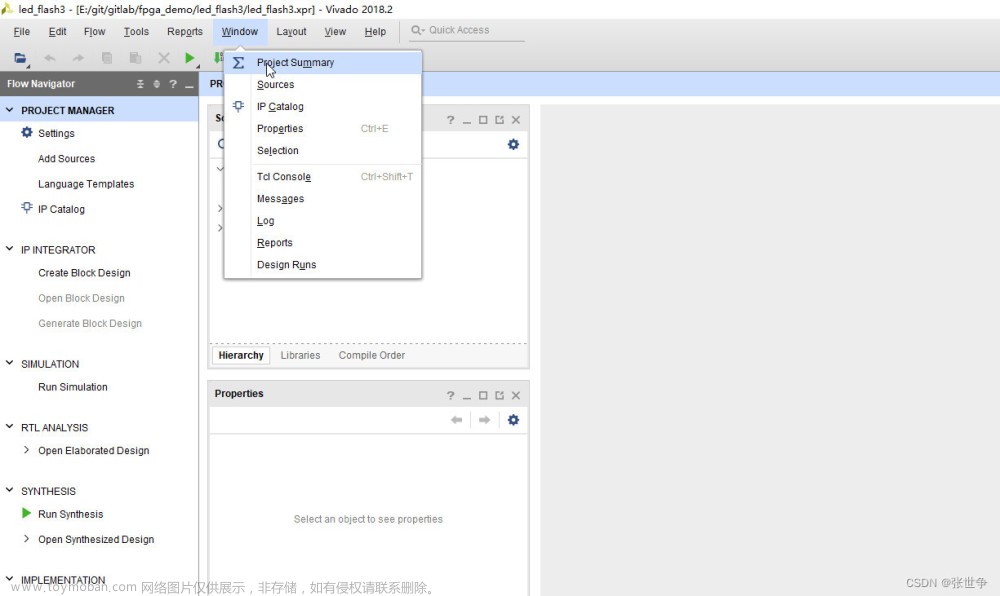

1、使用 谷歌浏览器 点击如下链接进入下载界面

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/archive.html

文章来源:https://www.toymoban.com/news/detail-518151.html

文章来源:https://www.toymoban.com/news/detail-518151.html

2、下一步,登陆你的XILINX账号,然后就可以下载了 文章来源地址https://www.toymoban.com/news/detail-518151.html

文章来源地址https://www.toymoban.com/news/detail-518151.html

到了这里,关于官网下载 Vivado的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!