前言

最近学习了在Quarus II 中运用嵌入式逻辑分析仪Singal Tap II 对数据波形进行抓取,对实现过程作一个记录和总结。本文就以之前写的串口收发程序作为样例,介绍Singal Tap II 的使用流程和步骤。

参考资料:《FPGA 实战开发指南》。

一、SingalTap II 是什么?

Singal Tap II 是一种嵌入到Quartus II 内部的逻辑分析仪,当RTL文件在仿真后没有问题,但是上板验证后又得不到正确的实验现象时,由于FPGA内部波形难以观察,常需要采用逻辑分析仪将内部信号引出。而外部逻辑分析仪存在着价格昂贵、FPGA端口数量不足、引脚间距小引出困难等问题。而Singal Tap II 则以低成本的方式解决了成本高、引出信号困难的问题,适用于仿真代码覆盖率未达到100%,多输入异步信号难以仿真以及存在芯片信号之间相互串扰等仿真难以解决的情况,将板上数据信号引出便于查找BUG。

二、使用流程

样例采用简单的串口收发模块,抓取其中的波形中间变量和输出端口数据以供观察。

1.创建SingalTap II 文件

先打开我们的样例工程文件,创建文件可以在tools–SingalTap II Logic Analyzer打开,也可以在File–New–SingalTap II Logic Analyzer File创建,

创建文件后将文件保存在工程文件夹下,此时会报输入信号为空,不用管它,继续保存。

进入到页面内部,页面主要分为四个部分:①:主要控制设备连接以及后续程序下载sof文件;②:信号配置界面,选择抓取波形的参考时钟、信号抓取的形式、信号触发的优先级等;③:显示抓取的Data数据以及设置抓取的触发条件;④:程序层级以及设计日志信息。

2.配置信号触发形式

首先配置系统时钟,点击下图选择系统时钟,在Named栏目写入系统时钟,在筛选器Filter中选中常用的SingalTap II:pre-synsynthesis,在顶层模块RS232中寻找,在左下方栏目中双击系统时钟,添加到右方,点击OK即可。

接下来配置信号采集方法以及采集深度:①:采样深度点击Sample depth 后的下拉,选择1K,采样的波形时间长度 = 采样深度 * 采样周期。由于SingalTap采集的波形数据需要FPGA内部的RAM空间来存储数据,所以这里采集深度合适就好,无需过大。RAM type 在芯片有多个RAM块时可以选择,这里我们选择默认;②:Segmented是分段式采集,每次满足设定的触发条件,采集一定数量的数据,直到采集满,以4 256 sample segments 为例,每次触发采集256个数据,可以循环触发四次。本次我们不勾选此项;③:存储类型,选择第一个continous连续进行采样。

设置触发条件:①:流程控制采用顺序控制,另外一个选项基于状态控制的方法适用于较为复杂的情况触发情况下;②:触发位置,选择pre trigger position 仅采集触发位置后方的数据;③:触发条件,我们设置为1个优先级别,如果设置多个优先级别,则会由最高级别优先触发后才会允许低级别的条件触发,当所有条件均触发以后才会进行数据的抓取。

3.选择待抓取信号

在图中双击空白处或者右击后选择Add Nodes,进入到以下界面:Named选择通配符 “ * ” ,筛选器选择SingalTap II:pre-synsynthesis,Look in : 在顶层文件中进行查找,点击list出现所有数据。

找到模块中我们需要观察的若干个数据,添加到右侧中,点击OK。

上述步骤完成后,setup 界面更新为下图:

4.设置信号触发条件

在setup界面进行触发条件的配置,其中右上角的触发条件可以选择各个数据的条件是与还是或,或是其他自定义的情况,本文选用常见的与条件,只有每个数据都满足触发条件才开始数据的采集。

其中每一个数据,右击选择触发的条件,其中:

Don’t Care:不关心

Low:低电平触发

Falling Edge:下降沿触发

Rising Edge:上升沿触发

High:高电平触发

Either Edge:上升沿或下降沿触发

我们这里将输入数据的接收模块中的start_flag设置为高电平触发,其他均设置为不关心;start_flag是检测rs232协议中开始位的低电平的标志位,当其拉高一个时钟周期后,开始进行串行数据到并行数据的转换。这样的话,只有当串口发送给下位机时,才会引起start_flag拉高,进而满足触发条件。

此外,因为现在的情况下,波形数据的抓取是在上电一段时间后才开始执行,有的信号仅在上电开始的较短时间内存在,可能会遗漏数据。因此,需要设置为上电后就使得触发器在准备触发状态,右击下图中Instance中的 auto_signaltap_0 右击选择Enable Power-Up Trigger,注意此时上述信号的触发条件需要重新进行设置,设置完成后回到工程文件界面对文件重新进行全编译。至此,触发条件基本配置完成。

5.上板提取信号

完成触发条件的配置后,连接好我们的FPGA开发板的电源、下载线、USB转串口线。在setup中选择下载器USB-Blaster,关闭选项框。

选中下载器以后,系统自动识别出了设备,接下来点击下图处,选择sof文件。

下载文件到开发板中,下载完成以后,这里的文件状态为:Not Running,即未运行。

先选中auto_singaltap_0,然后单击单次运行按钮,文件状态变为等待上电状态,上方显示程序正在运行。

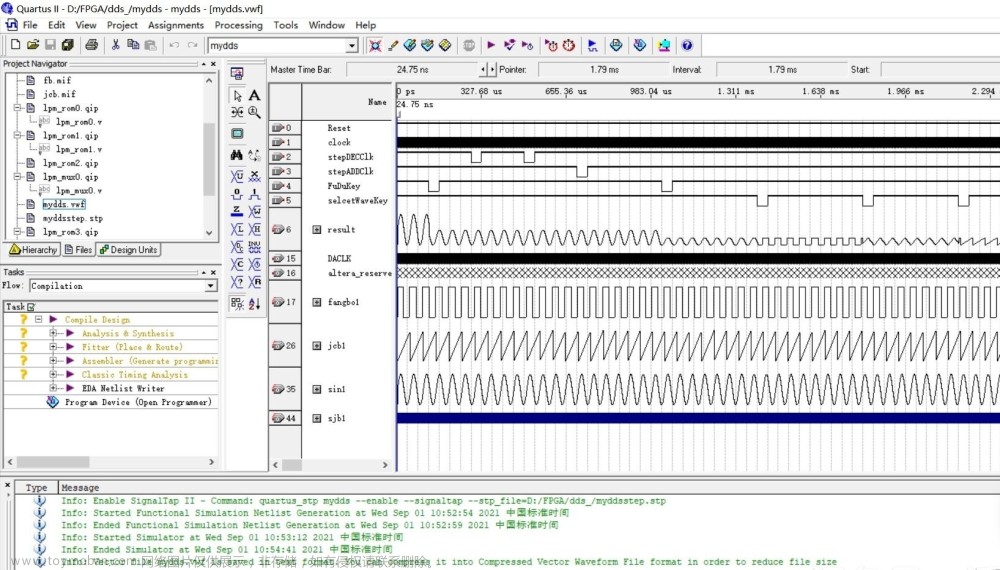

接下来打开上位机界面,配置好波特率9600,串口号,然后发送一串8位数据11223344,随后数据就被抓取并显示在data界面。

至此,我们已经能够抓取所需的波形并进行观察啦!

5.释放存储空间

之前提到,SingalTap II 是占用FPGA内部的RAM资源进行波形抓取的,所以在观察波形以后,有必要对占用的空间进行释放。从Assignments–settings–SignalTap II Logic Analyzer,取消勾选Enable SignalTap II Logic Analyzer 即可,取消勾选后占用的RAM资源即可释放。 文章来源:https://www.toymoban.com/news/detail-518616.html

文章来源:https://www.toymoban.com/news/detail-518616.html

总结

路漫漫其修远兮,要学习的还有很多呀,继续努力吧!文章来源地址https://www.toymoban.com/news/detail-518616.html

到了这里,关于【FPGA学习】使用SingalTap II 抓取波形的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!