本文分享XINES DSP+FPGA异构评估板,其中Xilinx Zynq-7000系列XC7Z035/XC7Z045系列主要特性,资源框图及PS端ETHRJ45接口引脚说明。

CPU架构:DSP+FPGA

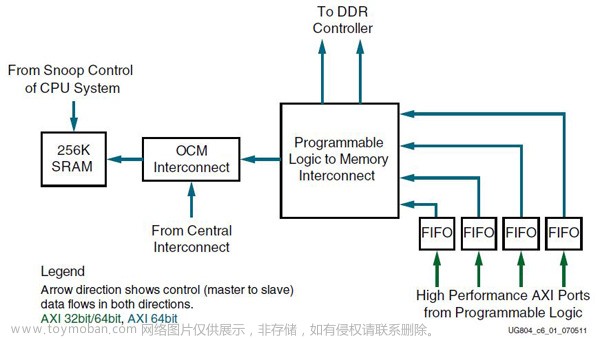

FPGA为Xilinx Zynq-7000 SoC,兼容XC7Z035/XC7Z045,平台升级能力强,以下为Xilinx Zynq-7000特性参数:

(数据手册见Datasheet目录)

ZYNQ7035 PS端ETH RJ45接口

评估板XQ6657Z35-EVM ,ZYNQ XC7Z035/45的PS端 引出了1路千兆网口,其引脚定义如下图:

文章来源:https://www.toymoban.com/news/detail-521756.html

文章来源:https://www.toymoban.com/news/detail-521756.html

文章来源地址https://www.toymoban.com/news/detail-521756.html

文章来源地址https://www.toymoban.com/news/detail-521756.html

到了这里,关于Xilinx Zynq-7000系列XC7Z035/XC7Z045高性能SoC处理器评估板PS端ETH RJ45接口的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!