交通灯设计:

1、设计原理

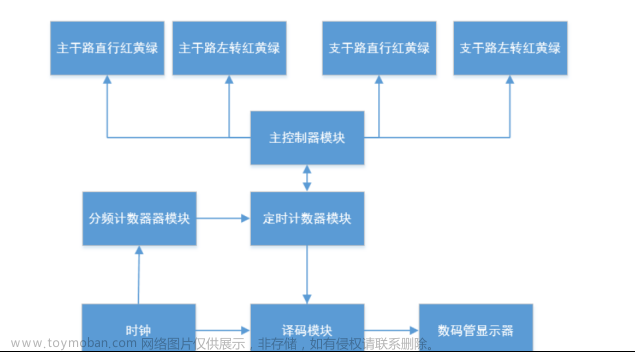

(1)对项目进行模块划分、对各模块的功能及其端口进行说明。

①分频器部分

降低实验板固有频率,分出频率用来计数和数码管动态扫描。

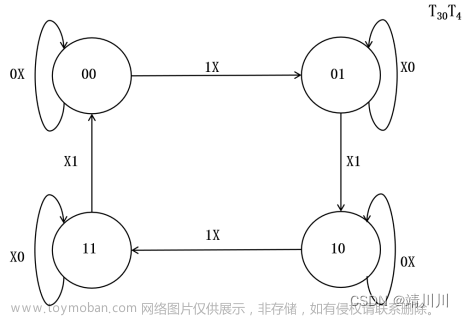

②状态机部分

0,1,2,3四个基础状态以及进一步完善后的检修和行人通行状态。

③LED灯与数码管显示部分

LED灯模拟东西南北方向交通灯的状况,数码管显示当前状态剩余时间。

2、设计源文件

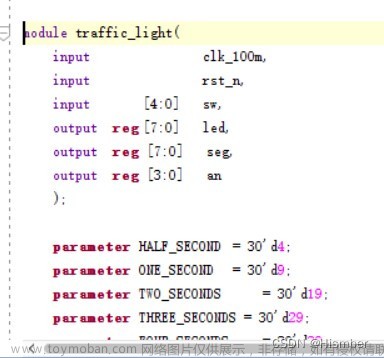

①主模块

`timescale 1ns / 1ps

module jiaotong(

input clk_100MHZ,

input rst,

input stby,//检修

output [7:0]dsmg, //数码管段选

output reg [1:0]wsmg, //数码管位选

output reg [5:0]led //led灯:J3 J2 K2(东西红黄绿),K1 H6 H5(南北红黄绿)

);

wire clk_1Hz;

wire clk_400Hz;

fenpin u1(clk_100MHZ,32'd50000000,clk_1Hz);

fenpin u2(clk_100MHZ,32'd125000,clk_400Hz);

integer second;

integer shijian; //秒数计数上限

reg [2:0]state; //状态

always @(state) //状态定义

begin

case (state)

0:begin led=6'b001100;shijian=40; end //state=0:001100,东西绿灯亮,南北红灯亮,40s

1:begin led=6'b010100;shijian=5; end //state=1:010100,东西黄灯亮,南北红灯亮, 5s

2:begin led=6'b100001;shijian=40; end

3:begin led=6'b100010;shijian=5; end

4:begin led=6'b010010;end //state=4:010010,东西黄灯亮,南北黄灯亮

5:begin led=6'b000000;shijian=3;end //state=5:000000,灯灭,延时3s

endcase

end

always @(posedge clk_1Hz )

begin

begin

if( rst == 1)

begin

second = 0;

state = 0;

end

else if (rst == 0 && stby == 1)

state = 4;

else if (rst == 0 && stby==0 && state == 4 )

second = 0;

end

if (state != 4)

second = second + 1;

if (shijian == second)

second = 0;

if (second==0)

begin

case (state)

0,1,2 : state <= state +1 ; //状态转换0-1-2-3-4-5-0

3 : state <= 0;

4 : state <= 5;

5 : state <= 0;

endcase

end

end

reg [2:0]wei;

reg [3:0]num;

shumaguang u3(num,dsmg);

//数码管显示

always @(posedge clk_400Hz)

begin

if(!wei)

wsmg=8'b00000001;

else

wsmg = wsmg << 1;

case(wei)

0:num=(shijian-second)%10; //数码管个位

1:num=(shijian-second)/10; //数码管十位

2:num=10;

3:num=10;

4:num=10;

5:num=10;

6:num=10;

7:num=10;

endcase

wei = wei + 1'b1;

end

endmodule

②分频器模块

module fenpin(

input clk_100MHZ,

input[31:0] div,

output reg clk_Hz

);

integer clk_cnt; //计数器的值

always @(posedge clk_100MHZ)

begin

if(clk_cnt==div)//判断计数器的值是否计数到div

begin

clk_cnt <= 1'b0;

clk_Hz <= ~clk_Hz;end //如果计数到div,计数器的值清零,同时clk_Hz的电平翻转一次,即分频后频率100MHz/div/2

else

clk_cnt <= clk_cnt + 1'b1;//计数没有到div,计数值加1

end

endmodule

③数码管模块

module shumaguang(

input [3:0]num,

output reg [7:0]dsmg

);

always @(*)

case (num)

0:dsmg <= 8'b00111111;

1:dsmg <= 8'b00000110;

2:dsmg <= 8'b01011011;

3:dsmg <= 8'b01001111;

4:dsmg <= 8'b01100110;

5:dsmg <= 8'b01101101;

6:dsmg <= 8'b01111101;

7:dsmg <= 8'b00000111;

8:dsmg <= 8'b01111111;

9:dsmg <= 8'b01101111;

10:dsmg <= 0;

endcase

endmodule

3、仿真测试文件文章来源:https://www.toymoban.com/news/detail-521828.html

`timescale 1ns / 1ps

module sim_jiaotongdeng( );

reg clk;

reg rst;

reg stby;//检修

wire[5:0]led;

jiaotong a1(.clk_100MHZ(clk),.rst(rst),.stby(stby),.led(led));

parameter PERIOD = 10; //固定计数周期

always begin

clk = 0;

#(PERIOD/2) clk = 1;

#(PERIOD/2);

end

initial begin

clk = 0;

rst = 1;

stby = 0;

#100;

rst = 0;

#100; //延时

stby = 1;

end

endmodule

仿真结果

实验板部分结果

文章来源地址https://www.toymoban.com/news/detail-521828.html

文章来源地址https://www.toymoban.com/news/detail-521828.html

到了这里,关于【FPGA】EDA技术综合设计 交通灯设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!