本文以余3码加法计数器的设计为例,说明仿真激励过程中遇到的问题,解决方法及分析。

加法器电路的实现代码如下:

module m10counterGU(clk,state);

input clk;

output reg [3:0]state;

//Excess-3 code

parameter S0=4'b0011,S1=4'b0100,

S2=4'b0101,S3=4'b0110,

S4=4'b0111,S5=4'b1000,

S6=4'b1001,S7=4'b1010,

S8=4'b1011,S9=4'b1100;

always @(negedge clk)

case (state)

S0:state<=S1;

S1:state<=S2;

S2:state<=S3;

S3:state<=S4;

S4:state<=S5;

S5:state<=S6;

S6:state<=S7;

S7:state<=S8;

S8:state<=S9;

S9:state<=S0;

default:state<=S0;

endcase

endmodule仿真激励文件1的代码如下:

module sim_m10counterGU( );

reg clk;

wire [3:0]state;

m10counterGU uu(clk,state);

initial begin clk = 1; end

always begin #10;clk = ~clk; end

endmodule仿真结果如下图所示:

这里,clk信号的初值设为1,得到的仿真结果,说明了,在clk的下降沿状态会发生转移。在前10ns,由于未出现下降沿,则状态值是不确定的。

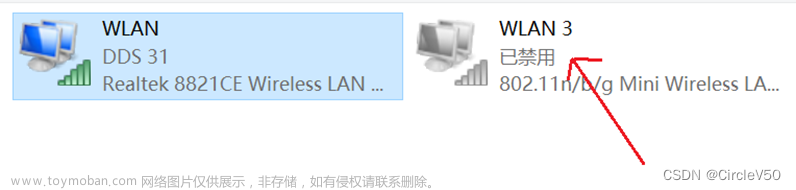

如果,在仿真激励文件中,将clk信号的初值设为0,见下面这个仿真激励文件2,则得到的结果如下:

module sim_m10counterGU( );

reg clk;

wire [3:0]state;

m10counterGU uu(clk,state);

initial begin clk = 0; end

always begin #10;clk = ~clk; end

endmodule

得到这个结果,说明,在vivado里仿真时,clk的低电平状态也会触发always语句块描述的电路去动作。此时,低电平状态跟下降沿的作用是相同的。因此,上图红色框标出的地方,在计数器从初值开始计数。

问题讨论:文章来源:https://www.toymoban.com/news/detail-522331.html

由于这个现象的存在,在进行仿真测试的时候,建议采用方法1进行测试。因为,采用方法2,会隐藏计数器初值设置功能必要性的问题。会造成这样的误解:就是不需要设置初值,计数器会自动开始从初值开始计数。文章来源地址https://www.toymoban.com/news/detail-522331.html

到了这里,关于关于Vivado仿真时,时钟信号初值设置方法导致仿真结果不一致的问题分析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![【常见 Error & Bug】Vivado仿真报错 ERROR: [XSIM 43-3322] 解决方法](https://imgs.yssmx.com/Uploads/2024/02/514419-1.png)