作为学习FPGA的小白一枚,总是在看论文的时候发现大牛们的内容中包含逻辑设计图也就是门电路的截图,而我自己在学习的时候看正点原子或者野火视频的时候没有发现这一部分(也有可能有,但我没全部看完系列视频,所以也就没发现),就上网搜索了这一部分内容,打算写篇小内容记录下来,主要是担心自己遗忘,有需要的同学也可以看看我这篇内容哦~

首先,根据我要做的东西,在老师的论文中找到了需要设计的门电路图。

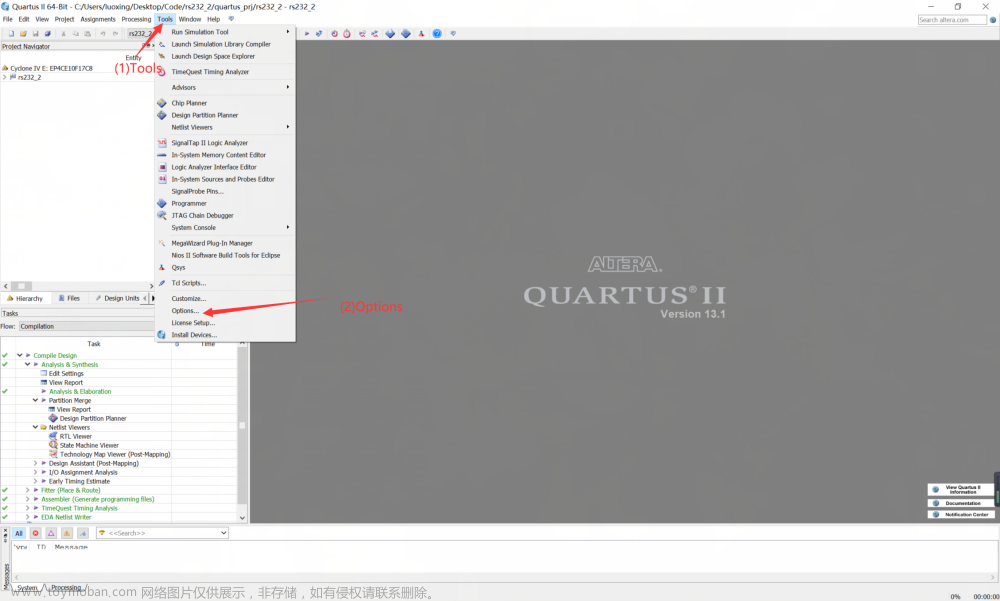

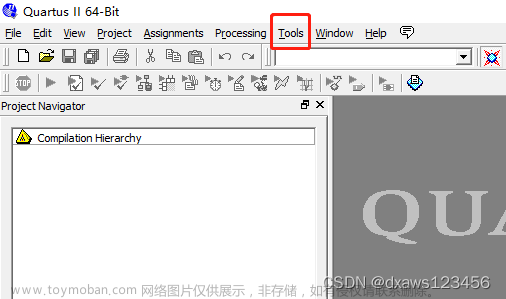

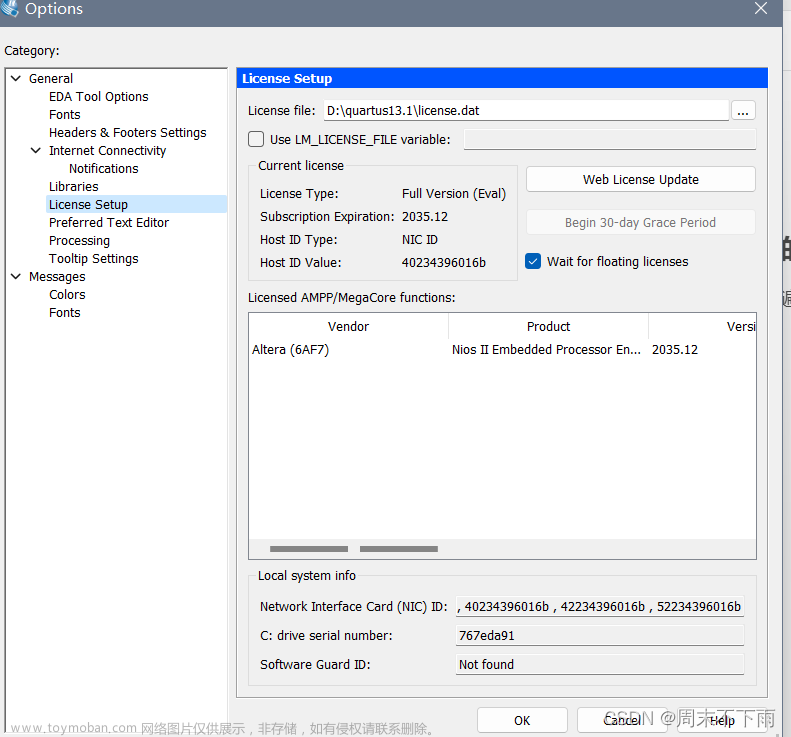

接下来是对在Quartus II 13.1软件内的操作步骤进行记录。

1.在新建完工程之后点击File->new->Design Files->Block Diagram/Schematic File

2.进入以下界面。

3.点击左上角Symbol Tool,点击primitives->logic->and2,这里我是以与门进行举例,需要什么器件就选择什么,选定之后点击OK,然后点击鼠标放置到界面内就可以了。

友情提示:Orthogonal Node Tool导线,引脚名称可通过双击进行修改。

最终我的逻辑设计图就搭建完成了~

文章来源地址https://www.toymoban.com/news/detail-522714.html文章来源:https://www.toymoban.com/news/detail-522714.html

到了这里,关于FPGA-Quartus II 13.1画逻辑门电路图的详细步骤的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!