VIVADO和MODELSIM联合仿真编译库问题

初次在VIVADO中使用MODELSIM仿真器,或仿真时由于编译库问题报错,可进行如下步骤,个人经验,源于百度,如有问题,请多多指教。

1. 打开VIVADO,在工具栏点击Tools->Compile Simulation Libraries

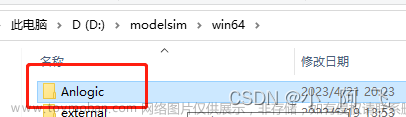

Compiled Library location处选择编译库存放的位置,可在任意处新建文件夹即可;Simulation executable path选择modelsim安装目录下win64文件夹,点击Compile进行编译。

2. 编译完成后,打开库路径下的modelsim.ini文件并找到“;mvc_lib = $MODEL_TECH/…/mvc_lib”,如下图所示:

下面即为编译好的IP所处的路径,将这些全部复制。

3. 然后打开modelsim安装路径下的modelsim.ini文件,取消只读属性,如下图所示:

4. 将其打开,找到“modelsim_lib = $MODEL_TECH/…/modelsim_lib”处粘贴添加ip库路径。

文章来源:https://www.toymoban.com/news/detail-523170.html

文章来源:https://www.toymoban.com/news/detail-523170.html

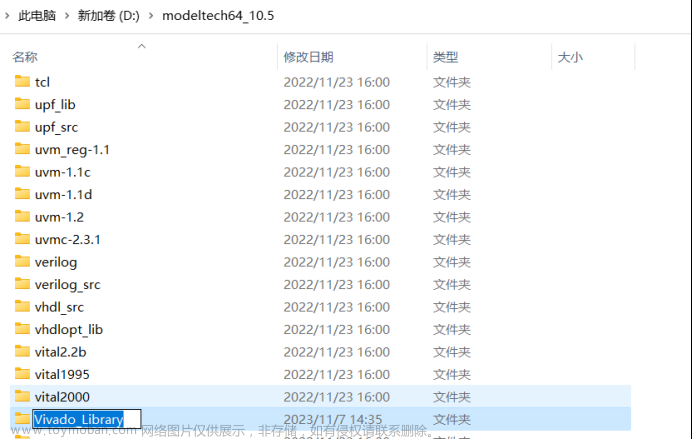

5.打开Modelsim软件,即可发现xilinx的ip全被加载进modelsim了。

在VIVADO进行仿真时,在设置中选择对应的编译库位置: 文章来源地址https://www.toymoban.com/news/detail-523170.html

文章来源地址https://www.toymoban.com/news/detail-523170.html

到了这里,关于VIVADO和MODELSIM联合仿真编译库问题的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!