1 简介

上电时序,也叫做Power-up Sequence,是指电源时序关系。下面就是一系列电源的上电的先后关系:

2 方案介绍

2.1 电容实现延时

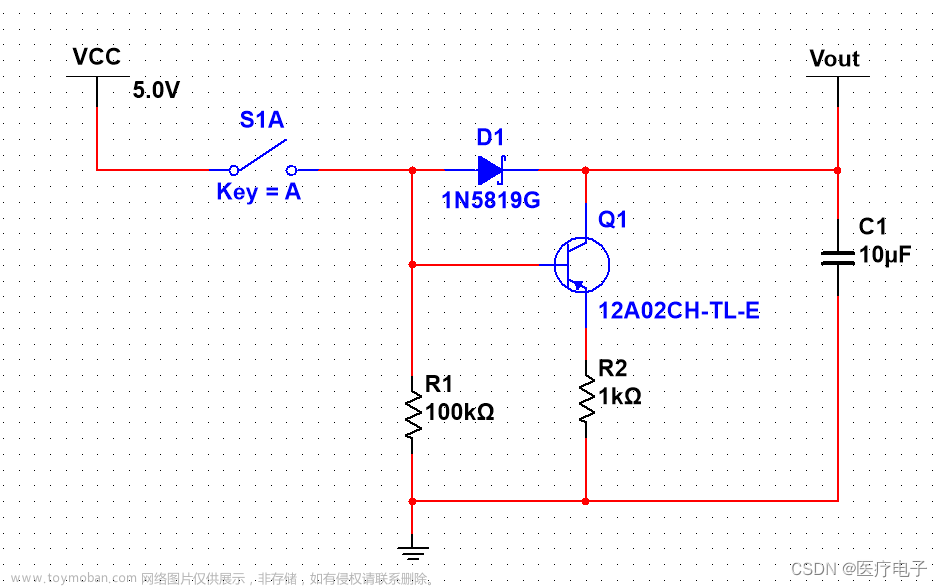

采用不同的电容来控制上电延时时间的长短,具体的电路见下图:

这种上电时序控制的方式,电路结构简单,但是延时时间难以精确的控制。在FPGA的电源时序控制中,应用十分广泛。

2.2 芯片控制延时

我们采用的LM3880芯片进行电源时序控制,这种控制的方式比较简单。LM3880 简单电源时序控制器提供了最简单的方法来控 制多个独立电压轨的上电时序和下电时序。通过错开启 动序列,可以避免可能影响系统可靠性的锁存情况或大 浪涌电流。

2.2.1 上电/下单控制

上电与下单的延时时间由EN管脚进行控制,默认是2ms,上电/下电的时序图见下:

-

上电序列

-

下电时序

2.2.2 延时时间计算

如需对 VCC 电压轨提供额外的延迟序列,在 EN 引脚上连接一个电容,见下图:

在使用内部上拉电流源为外部电容 (CEN) 充电的情况下,可通过下面公式来计算使能引脚延迟:

第一个计时器将在上升阈值开始计数,但始终会在第一个输出标志 释放之前 EN 引脚取消置位时复位。

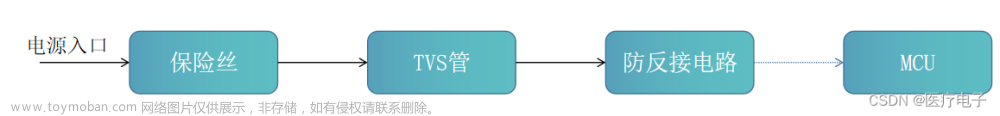

3 建议

-

电源建议

VCC 引脚应尽可能靠近输入电源 (2.7–5.5V)。不需要使用输入电容,但建议在 VCC 引脚上存在噪声时使用输入电 容。可以使用 0.1μF 陶瓷电容器来旁路该噪声。

-

布局建议

-

应在标志输出引脚和正输入电源(通常为 VCC)之间连接上拉电阻。也可以使用独立的标志电源。这些电阻应 尽可能靠近简单电源时序控制器和标志电源。建议使用最短的迹线进行连接。上拉电阻器的典型值是 100kΩ。文章来源:https://www.toymoban.com/news/detail-523356.html

-

对于非常严格的时序要求,应使用最短且长度相等的连线将标志输出连接到所需的输入。这将减少线路上标志 输出之间的任何传播延迟和时序误差。文章来源地址https://www.toymoban.com/news/detail-523356.html

到了这里,关于数字电路硬件设计系列(十七)之上电时序控制电路的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!