全加器

输入原理图实现

半加器

什么是半加器?

半加器是能够对两个一位的二进制数进行相加得到半加和以及半加进位的组合电路。

半加器的真值表

半加器表达式:

半加器电路图:

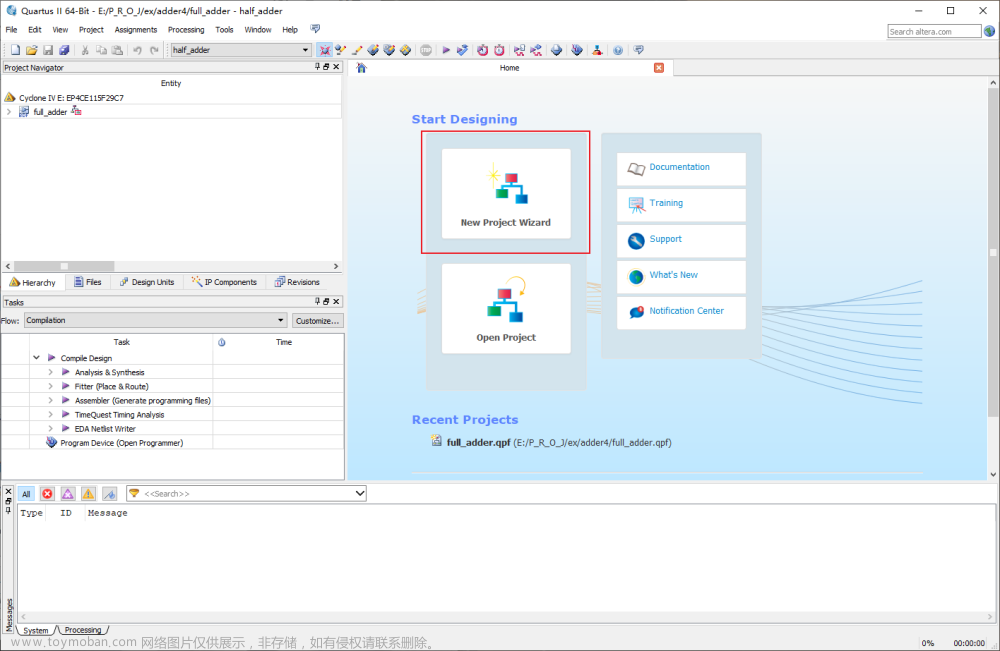

建立原理图

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

现在,你已经可以创建了一个工作空间,让我们开始绘制原理图吧。

从以下路径可以添加一张原理图的画布:首先选择File->New,进入后选择Block Diagram/Schematic File

在画框的上方可以添加你想要的逻辑门器件。

输入逻辑门的英文名则可以查找对应器件。

添加其余部件,绘制半加器的原理图。

保存并编译得到一张漂亮的原理图。

模拟仿真:

创建一个向量波形文件,选择菜单项 File→New->VWF。

在波形文件编辑器左端大片空白处双击,出现“insert node or bus”对话框,点击“node finder”按钮。

添加信号

”>>“选项可以一键添加信号。

编辑信号:

选中一段波形,再点击按钮,可以改变电平。

保存文件并启动功能仿真,

结果如下

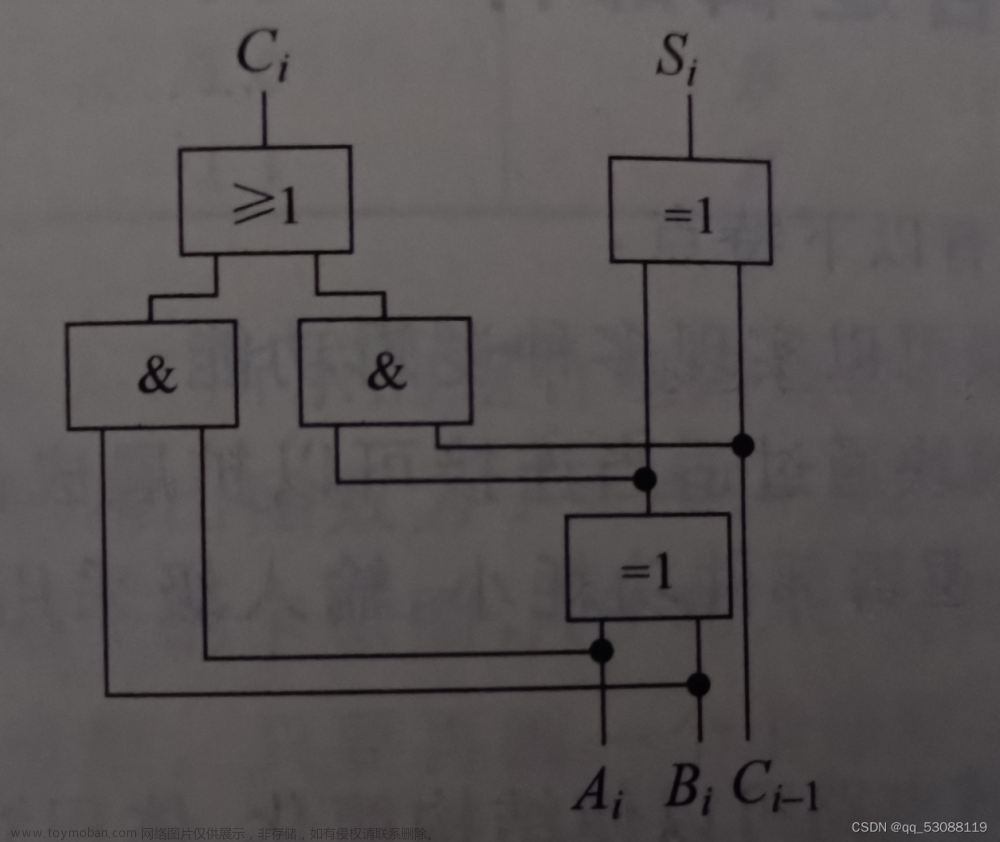

全加器

全加器真值表:

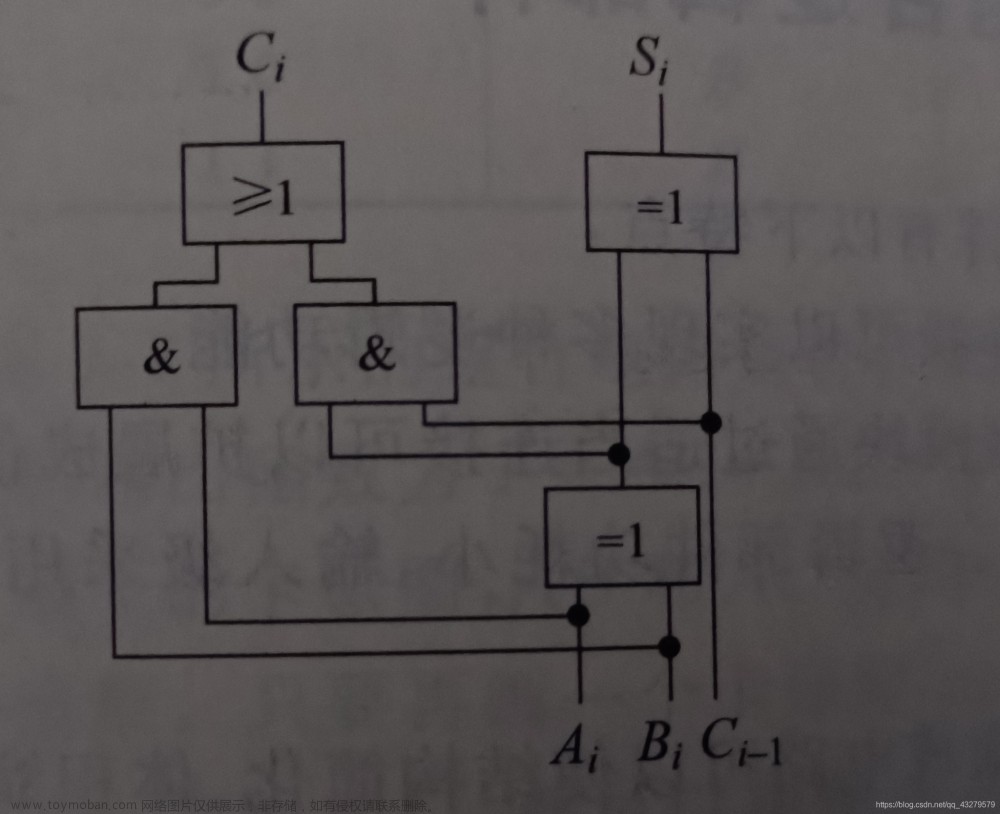

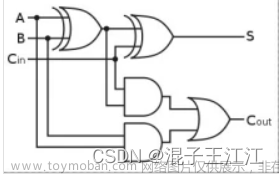

全加器电路图:

绘制原理图

前文已经制作了一个半加器,接下来,我们将要利用它作为可以调用的原件绘制全加器的原理图。

在选择器件的位置搜索半加器的文件名,则可以调用我们制作的半加器原理图。

添加其余部件,绘制原理图:

将全加器设置为顶层文件,改变顶层实体后要重新进行综合,然后才能对当前顶层实体进行波形仿真等操作。

保存编译,可以查看原理图

按照前文的步骤进行仿真模拟:

Verilog编程实现

新建一个项目。

代码:

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

保存编译,查看原理图

模拟仿真:

烧录

查看开发板引脚图,找到相关引脚,将需要使用的引脚,绑定到原理图上对应的输入处

绑定引脚

绑定成功。

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮 ,则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USBblaster”,再点击“ok”,则硬件被安装上。

安装好硬件后,在下载的.sof文件后打钩,再点击start,看到100%(successful),下载成功

4位全加器

原理图

将1位全加器保存为元件,搭建4位全加器,添加其余部件完成4位全加器原理绘制。

保存编译,查看原理图

模拟仿真。

Verilog编程实现

代码:

module full_adder4(

input[3:0] a,b,

input cin,

output[3:0] sum,

output cout

);

assign{cout,sum} = a+b+cin;

endmodule

保存编译查看原理图。

模拟仿真

总结与参考

加深了对Quantus的认识,在实验过程中,有遇到无法查找到目标芯片,无法查找到Modelsim从而造成的无法模拟仿真等问题,在寻求帮助以及查找资料过后都一一解决,极大地提高了我的耐心,加深了对半加器,全加器的认识。

https://blog.csdn.net/qq_43279579/article/details/115480406文章来源:https://www.toymoban.com/news/detail-523490.html

https://zhuanlan.zhihu.com/p/150674799文章来源地址https://www.toymoban.com/news/detail-523490.html

到了这里,关于【FPGA实验一】半加器全加器实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!