PLL的英文全称是Phase Locked Loop,即锁相环,是一种反馈控制电路。PLL对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。Xilinx 7系列器件中的时钟资源包含了时钟管理单元CMT,每个CMT由一个MMCM和一个PLL组成。对于一个简单的设计来说,FPGA整个系统使用一个时钟或者通过编写代码的方式对时钟进行分频是可以完成的,但是对于稍微复杂一点的系统来说,系统中往往需要使用多个时钟和时钟相位的偏移,且通过编写代码输出的时钟无法实现时钟的倍频,因此学习Xilinx MMCM/PLL IP核的使用方法是我们学习FPGA的一个重要内容。

11.1MMCM/PLL IP核简介

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

Xilinx 7系列器件中具有时钟管理单元CMT时钟资源,xc7z020芯片内部有4个CMT,xc7z010芯片内部有2个CMT,为设备提供强大的系统时钟管理以及高速I/O通信的能力。时钟管理单元CMT的总体框图如下图所示。

图 11.1.1 CMT总体框图

MMCM/PLL的参考时钟输入可以是IBUFG(CC)即具有时钟能力的IO输入、区域时钟BUFR、全局时钟BUFG、GT收发器输出时钟、行时钟BUFH以及本地布线(不推荐使用本地布线来驱动时钟资源)。在最多的情况下,MMCM/PLL的参考时钟输入都是来自IBUFG(CC)即具有时钟能力的IO输入,本实验也是如此。MMCM/PLL的输出可以驱动全局时钟BUFG和行时钟BUFH等等。BUFG能够驱动整个器件内部的PL侧通用逻辑的所有时序单元的时钟端口。BUFG/BUFH/CMT在一个时钟区域内的连接框图如下图所示。

图 11.1.2 BUFG/BUFH/CMT在一个时钟区域内的连接

有关Xilinx时钟资源和CMT的更详细信息,读者后期可以花一些时间和精力去学习一下Xilinx官方的手册文档“UG472,7 Series FPGAs Clocking Resources User Guide”里的介绍。

MMCM和PLL的总体框图如下图所示。

图 11.1.3 MMCM总体框图

图 11.1.4 PLL总体框图

其中MMCM的功能是PLL的超集,其具有比PLL更强大的相移功能。MMCM主要用于驱动器件逻辑(CLB、DSP、RAM等)的时钟。PLL主要用于为内存接口生成所需的时钟信号,但也具有与器件逻辑的连接,因此如果需要额外的功能,它们可以用作额外的时钟资源。

PLL由以下几部分组成:前置分频计数器(D计数器)、相位-频率检测器(PFD,Phase-Frequency Detector)电路,电荷泵(Charge Pump)、环路滤波器(Loop Filter)、压控振荡器(VCO,Voltage Controlled Oscillator)、反馈乘法器计数器(M计数器)和后置分频计数器(O1-O6计数器)。

在工作时,PFD检测其参考频率(FREF)和反馈信号(Feedback)之间的相位差和频率差,控制电荷泵和环路滤波器将相位差转换为控制电压;VCO根据不同的控制电压产生不同的震荡频率,从而影响Feedback信号的相位和频率。在FREF和Feedback信号具有相同的相位和频率之后,就认为PLL处于锁相的状态。

在反馈路径中插入M计数器会使VCO的震荡频率是FREF信号频率的M倍,FREF信号等于输入时钟(FIN)除以预缩放计数器(D)。参考频率用以下方程描述:FREF= FIN/D,VCO输出频率为FVCO= FIN*M/D,PLL的输出频率为FOUT=(FIN*M)/(N*O)。

Xilinx提供了用于实现时钟功能的IP核Clocking Wizard,该IP核能够根据用户的时钟需求自动配置器件内部的CMT及时钟资源,以实现用户的时钟需求。在这里我们主要讲解的是如何使用该IP核,有关该IP核的更详细介绍,读者可以参阅Xilinx官方的手册文档“PG065,Clocking Wizard v6.0 LogiCORE IP Product Guide”。

11.2实验任务

本节实验任务是使用Zynq开发板输出4个不同时钟频率或相位的时钟,并在Vivado中进行仿真以验证结果,最后生成比特流文件并将下载到开发板上,使用示波器来测量时钟的频率。

打开“IP Catalog”窗口后,在搜索栏中输入“clock”关键字,可以看到Vivado已经自动查找出了与关键字匹配的IP核名称,如下图所示。

接下来就是配置IP核的时钟参数。最上面的“Component Name”一栏设置该IP元件的名称,这里保持默认即可。在第一个“Clocking Options”选项卡中,“Primitive”选项用于选择是使用MMCM还是PLL来输出不同的时钟,对于我们的本次实验来说,MMCM和PLL都可以完成,这里我们可以保持默认选择MMCM。需要修改的是最下面的“Input Clock Information”一栏,把“Primary”时钟的输入频率修改为我们开发板的核心板上的晶振频率50MHz,其他的设置保持默认即可,如下图所示。

接下来切换至“Output Clocks”选项卡,在“Output Clock”选项卡中,勾选前4个时钟,并且将其“Output Freq(MHz)”分别设置为100、100、50、25,注意,第2个100MHz时钟的相移“Phase(degrees)”一栏要设置为180。其他设置保持默认即可,如下图所示。

Port Renaming”选项卡主要是对一些控制信号的重命名。这里我们只用到了锁定指示locked信号,其名称保持默认即可,如下图所示。

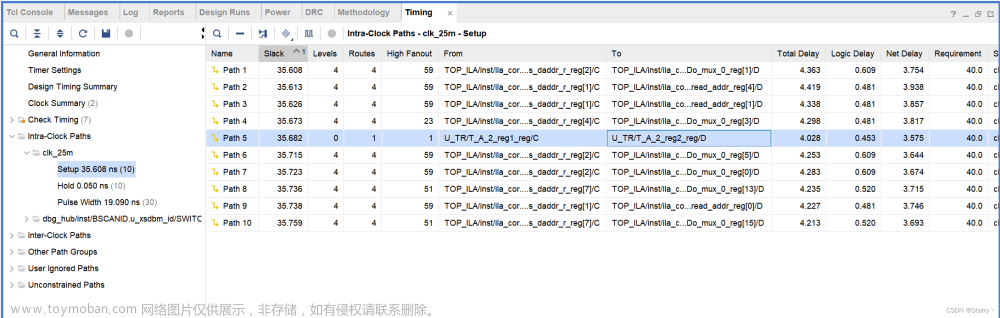

“MMCM Setting”选项卡展示了对整个MMCM/PLL的最终配置参数,这些参数都是根据之前用户输入的时钟需求由Vivado来自动配置,Vivado已经对参数进行了最优的配置,在绝大多数情况下都不需要用户对它们进行更改,也不建议更改,所以这一步保持默认即可,如下图所示。文章来源:https://www.toymoban.com/news/detail-523775.html

文章来源地址https://www.toymoban.com/news/detail-523775.html

文章来源地址https://www.toymoban.com/news/detail-523775.html

到了这里,关于Vivado clocking wizard IP核PLL/MCMM配置的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!