UVM实战中实例源码下载:https://www.hzcourse.com/web/refbook/detail/5651/229

一、环境配置

终于配置跑通 UVM实战中的实例了,下面是基于linux+vcs+verdi的环境配置

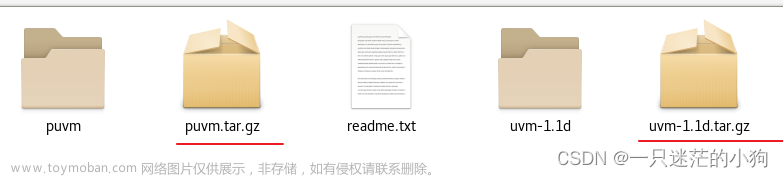

1、将下载的源码文件夹解压后共享到虚拟机中

2、需要重新配置setup.vcs文件

原始文件:

#!/bin/csh

setenv VCS_HOME /opt/vcs/E-2011.03

setenv UVM_HOME ~/uvm/uvm-1.1d

setenv WORK_HOME `pwd`

setenv SIM_TOOL VCS

set path = (/opt/vcs/E-2011.03/bin ${WORK_HOME}/bin $path)说明:

- 这个配置文件是基于csh的,安装的虚拟机不一定支持,支持bash。

修改文件:

#!/bin/bash

export VCS_HOME=/opt/synopsys/vcs

export UVM_HOME=/home/host/verify/example_and_uvm_source_code/uvm-1.1d/

export WORK_HOME=/home/host/verify/example_and_uvm_source_code/puvm

export SIM_TOOL=VCS

export NOVAS_HOME=/opt/synopsys/verdi

export PATH=/opt/synopsys/vcs/linux64/bin:$PATH说明:

- vcs_home:vcs的安装路径

- uvm_home:uvm库文件的路径

- work_home:执行代码的工作路径

- sim_tool:设置使用的仿真工具是vcs

- novas_home:verdi的安装路径

- path:脚本的路径

- 修改完后要source setup.vcs

3、run文件配置

#!/bin/csh

if ( $SIM_TOOL == "QUESTA" ) then

vlib work

vlog -f filelist.f

vsim -sv_lib $UVM_DPI_DIR/uvm_dpi -do $WORK_HOME/bin/vsim.do -c top_tb

endif

if ( $SIM_TOOL == "VCS" ) then

vcs -sverilog $UVM_HOME/src/dpi/uvm_dpi.cc -CFLAGS -DVCS -timescale=1ns/1ps -f filelist.f

./simv

endif

if ( $SIM_TOOL == "NCSIM" ) then

ncverilog +sv -f filelist.f -licqueue -timescale 1ns/1ps -uvm -uvmhome $UVM_HOME

endif说明:

- sim_tool:对应不同的仿真工具,在setup.vcs中设置的是vcs

- 但不能直接使用这个run文件,需要修改

- 使用Makefile来运行

4、Makefile

使用makefile用着更习惯

UVM_HOME = /home/host/verify/example_and_uvm_source_code/uvm-1.1d/

elab:

vcs -top top_tb -full64 -lca -sverilog -debug_access+all -timescale=1ps/1ps -sim_res=1ps -kdb \

$(UVM_HOME)/src/dpi/uvm_dpi.cc -CFLAGS -DVCS \

+incdir+$(UVM_HOME)/src $(UVM_HOME)/src/uvm.sv \

-f filelist.f \

-LDFLAGS"-Wl,--rpth,$(NOVAS_HOME)/share/PLI/VCS/LINUX64"

run:

./simv &

verdi:

verdi -ssf ./tb.fsdb &

clean:

\rm -rf AN.DB

\rm -rf *simv*

\rm -rf DVEfiles

\rm -rf ucli.key

all: clean elab run说明:文章来源:https://www.toymoban.com/news/detail-524162.html

- 设置uvm_home的路径

- elab中要把UVM的库文件incdir进来,设置了top顶层是top_tb

- 若UVM的库文件就在VCS的安装路径下面可以直接用-ntb_opts uvm

- 需要修改filelist和把dut.sv包含到对应的路径中

- 在原始的top_tb.sv文件中加入下列initial代码

- 先删掉原本的run文件,执行make all 再make verdi 即可以用verdi看波形

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars;

end

(修改后的)2.2.1代码运行结果:

文章来源地址https://www.toymoban.com/news/detail-524162.html

文章来源地址https://www.toymoban.com/news/detail-524162.html

到了这里,关于(一)UVM验证平台搭建1的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!