优化二:减少命中时间的方式预测

路预测是一种高速缓存优化技术,它在高速缓存中保存额外的位来预测下一次高速缓存访问的路(或者组内的块)。这种预测可以提前设置多路选择器来选择期望的块,并且在那个时钟周期内,只进行一次标记比较,同时读取高速缓存数据。如果预测正确,高速缓存访问延迟就是快速命中时间。如果不正确,就尝试另一个块,改变路预测位,并且延迟多一个时钟周期。路预测可以减少冲突不命中,同时保持直接映射高速缓存的命中速度。

模拟表明,两路组相联高速缓存的组预测准确度超过 90%,四路组相联高速缓存的组预测准确度超过 80%,I 高速缓存的准确度高于 D 高速缓存。

I高速缓存和D高速缓存是指L1级别的高速缓存,分别用于缓存指令和数据。它们的作用是加速CPU对内存的访问,提高程序的执行效率。I高速缓存和D高速缓存一般是私有的,每个CPU核心都有自己的I高速缓存和D高速缓存。它们的容量一般比较小,通常在几十KB到几百KB之间。

I高速缓存和D高速缓存之间可能存在一致性问题,即当数据被修改为指令时,I高速缓存和D高速缓存中的内容可能不同步。这种情况一般发生在自修改代码(self-modifying code)或者调试器(debugger)等场景中。为了解决这个问题,可以采用硬件或者软件的方法来维护一致性。硬件方法是让I高速缓存和D高速缓存之间进行通信,每次修改数据时,检查并更新I高速缓存中的内容。软件方法是让操作系统在修改数据时,清除D高速缓存中的内容,并使I高速缓存中的内容失效,从而保证从主存中读取新的指令。

路预测还可以扩展为一种形式来降低功耗,通过使用路预测位来决定实际访问哪个高速缓存块(路预测位本质上是额外的地址位);这种方法,也许可以叫做路选择(way selection),在路预测正确时节省功耗,但是在路预测错误时增加了很多时间,因为访问,而不仅仅是标记匹配和选择,必须重复。这种优化可能只适合低功耗处理器。路选择的一个重要缺点是它使得很难流水线化高速缓存访问;然而,随着能源问题的增加,不需要给整个高速缓存供电的方案变得更有意义。

不能流水化原因:每个访问都可能需要两个时钟周期,而不能在一个时钟周期内完成。

优化三:流水线访问和多组缓存以增加带宽

这些优化方法都是通过流水线化高速缓存访问或者增加高速缓存的多路并行性来提高高速缓存的带宽;这些优化方法相当于超流水线和超标量技术提高指令吞吐量的对偶。

超流水线和超标量技术是两种提高CPU性能的技术,它们都利用了指令级并行的思想,但是实现方式不同。

超流水线技术是通过将每个流水线阶段细分为更小的子阶段,从而缩短机器周期,提高时钟频率,使得在相同的时间内执行更多的指令。超流水线技术可以看作是流水线技术的一种延伸,它不需要增加太多的硬件资源,但是会增加流水线级数,从而增加分支预测错误和数据相关的开销。

超标量技术是通过在CPU中设置多条流水线,并且每个时钟周期内可以发射和执行多条指令,从而提高指令吞吐率。超标量技术可以看作是标量流水线技术的一种扩展,它需要增加硬件资源的重复,例如多个取指、译码、执行和写回部件,并且需要由硬件来完成指令调度。

这些优化方法主要针对L1级别的高速缓存,因为访问带宽限制了指令吞吐量。多路并行也用在L2和L3级别的高速缓存中,但主要是作为一种功耗管理技术。流水线化L1可以提高时钟周期,但代价是增加了延迟。例如,Intel Pentium处理器在1990年代中期的指令高速缓存访问流水线需要1个时钟周期;Pentium Pro到Pentium III在1990年代中期到2000年的需要2个时钟周期;Pentium 4在2000年推出的和当前的Intel Core i7需要4个时钟周期。

流水线化指令高速缓存实际上增加了流水线阶段的数量,导致错误预测分支的惩罚更大。相应地,流水线化数据高速缓存导致发出加载指令和使用数据之间的时钟周期更多。

今天,所有的处理器都使用一些L1的流水线化,即使只是为了简单地分离访问和命中检测,而且许多高速处理器有三个或更多级别的高速缓存流水线。流水线化指令高速缓存比数据高速缓存更容易,因为处理器可以依赖高性能的分支预测来限制延迟效应。许多超标量处理器可以每个时钟周期发出和执行多于一个内存引用。

为了处理每个时钟周期多个数据高速缓存访问,我们可以将高速缓存划分为独立的路,每一路支持一个独立的访问。路最初用来提高主存储器的性能,并且现在用在现代DRAM芯片以及高速缓存中。

路并行工作得最好是当访问自然地分布在各路上,所以地址到路的映射影响了内存系统的行为。一个简单的映射方法是将块的地址顺序地分布在各路上,叫做顺序交错(sequential interleaving)。例如,如果有四路,路0有所有地址模4等于0的块,路1有所有地址模4等于1的块,以此类推。

多路并行也是一种降低高速缓存和DRAM功耗的方法。多路并行也用在L2或者L3级别的高速缓存中,但是出于不同的原因。有了多路并行的L2,我们可以处理多于一个未完成的L1不命中,如果各路没有冲突。

多路并行技术和多路关联技术的区别是:文章来源:https://www.toymoban.com/news/detail-524679.html

多路并行技术是指在一个程序中,将一个任务划分为多个子任务,让它们在不同的处理器或线程上同时执行,以提高程序的运行效率和响应速度。

多路关联技术是指在一个处理器中,设置多条流水线,并且每个时钟周期内可以选择其中一条流水线发射和执行一条指令,以提高处理器的指令吞吐率。文章来源地址https://www.toymoban.com/news/detail-524679.html

到了这里,关于计算机体系结构基础知识介绍之缓存性能的十大进阶优化之减少命中时间和流水线访问和多组缓存增加带宽(三)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

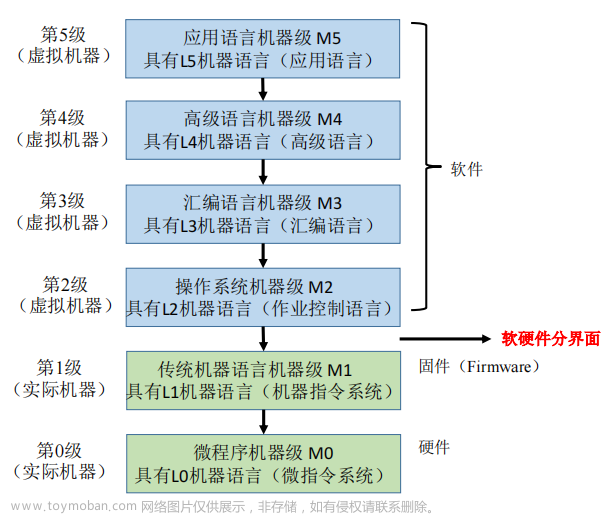

![[Linux]计算机软硬体系结构](https://imgs.yssmx.com/Uploads/2024/02/647238-1.png)